What you’ll learn

- What is CXL-attached memory?

- What is memory pooling?

- How Leo Smart Memory Controllers work with processors.

There’s never enough memory. Applications like cloud computing need as much as they can get. Processors tend to support a few banks of DRAM, and linking multiple processors together helps boost the amount of memory. Nonetheless, more is needed.

PCI Express is the de facto peripheral standard. Built on top of the latest standard is the Compute Express Link (CXL) standard, now in its third incarnation. It can be used to connect processors of all types and memory in a single memory space, allowing pools of memory to be allocated among compute resources.

Such a hyperscaler approach is where cloud computing is going, and it will be applicable to large embedded systems as well. Systems can create partitions with the required amount of memory, compute, and connectivity from a common pool of resources.

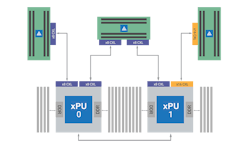

Astera Labs’ Leo Memory Connectivity Platform is designed to support CXL 1.1 and 2.0 (see figure). The Leo Memory Controller chip supports up to 2 TB of memory running at 5600 Mtransactions/s/memory channel. The chip supports JEDEC DDR standards as well as vendor-specific interfaces.

The system also provides server-grade customizable Reliability, Availability and Serviceability (RAS) capabilities. As a result, center operators can customize their systems so that factors such as memory errors, material degradation, environmental impacts, and manufacturing defects don’t impact applications. The telemetry and software APIs support fleet management of cloud-based platforms.

The latest products include the Leo E-Series Smart Memory Controllers that support memory expansion; the Leo P-Series Smart Memory Controllers supporting memory expansion, pooling, and sharing; and the Aurora A-Series Smart Memory Hardware Solutions, which is a PCIe CEM add-in card for plug-and-play deployment.