How Embedded Memory Will Drive an Emerging Technology to Success

What you'll learn:

- What emerging technologies are gearing up to potentially take over the memory space?

- The current status of NOR flash and SRAM.

- The overriding factor of cost and its impact on a technology's success.

The memory business is at a strange turning point. DRAM process migrations seem to have slowed and there’s talk of going 3D… NAND flash has already gone through a relatively painful 3D transition and is now performing extremely well as a 3D memory… and CMOS logic has reached process geometries that can’t support on-chip memory.

“WHAT?” you say about that last point. What has that to do with discrete memory chips, and who says that memory can’t be supported on CMOS logic? Well, that’s an important point, so let’s give it a look.

NOR Flash Stops at 28 nm

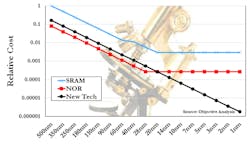

Most MCUs include NOR flash for their code store, as do many other SoCs. NOR is cheap, and it’s available on nearly all foundry CMOS logic processes. This has been the case for decades. But nobody has developed a way to make inexpensive NOR flash on a FinFET process, so NOR is unavailable at process geometries finer than 28 nm. This shows as the leveling off of the red line in Figure 1, which represents the relative cost of embedded NOR across process shrinks.

That leveling off might not present a problem if MCUs don’t migrate past 28 nm, and as long as none of the other SoCs that use NOR scale past 28 nm. History tells us that this is unlikely.

Some MCU designs that have already passed 28 nm use external serial NOR chips to carry code that’s downloaded on demand to SRAM caches on the MCU. While that can get expensive, since SRAM used six transistors per bit and NOR uses only one, it solves the current problem, and serial NOR chips are pretty cheap.

But that’s only a temporary solution, as SRAM also is challenged.

SRAM isn’t Far Behind

As processes shrink, it becomes increasingly challenging to make SRAM shrink along with the process. The IEEE International Solid State Circuits Conference (ISSCC) tracks SRAM bit sizes in a historical chart that’s updated every year.

The data in this chart, which runs from 90 nm to 5 nm, shows that the area of SRAM cells in research chips has shrunk an average of 17% per process node while the process has shrunk an average of 21%. At around 20 nm, in some processes, SRAM size and cost stops shrinking altogether (blue line in Fig. 1). Either way, it’s less economical to shrink SRAM than it is logic, rendering the SRAM increasingly costly (as a share of overall chip costs) over time.

The industry seems to need a new memory technology that will allow designers to shrink their MCUs and SoCs with process advances and not have to worry about re-architecting their memory system or putting up with a sub-optimal cost improvement.

Is there something that can be used to solve this conundrum?

Emerging Memories to the Rescue

In fact, there is, and it comes in the form of emerging memories—those memories that aren’t mainstream today, but could allow the industry to continue to reduce chip costs through process shrinks (black line in Fig. 1). These emerging memories are the subject of a new report from Objective Analysis and Coughlin Associates: Emerging Memories Enter Next Phase. This article is based on a small fraction of the information contained in the 231-page report.

The leading emerging memory technologies today are PCM, MRAM, FRAM, and ReRAM. Each is already in production and has shipped for over five years. Several others are in development in the hope of making their mark on the industry.

In their discrete form, as standalone memory chips, these products have sold into niches, and haven’t made great inroads largely due to cost. A paradox is preventing them from making great inroads: They must be cheaper than a mainstream memory (DRAM, SRAM, NOR and NAND flash, and EEPROM) to gain mass acceptance, but until they ship in volumes comparable to the established technologies, they will remain costlier than these established technologies. For years, this has prevented their growth and relegated them to market niches.

However, in embedded applications like MCUs and SoCs, where there’s a brick wall preventing the use of NOR flash, these technologies are gaining acceptance. It’s also likely that their wafer volume will undergo a dramatic increase in the near future.

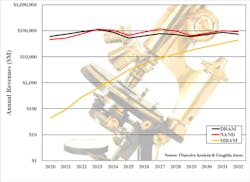

With this understanding, we have been able to compile a 10-year forecast for memory revenues that projects the annual revenues for both embedded and standalone emerging memories shown in Figure 2, which was taken from the report. We had to use a semi-logarithmic chart to allow the early years to simply show up, since they are so small today.

The chart shows the emerging memory as MRAM, but in reality, it’s too soon to tell which technology will actually win the race. What we know is that there’s room for only one of these to succeed in a big way, and the others will continue to serve market niches.

While NAND flash and DRAM revenues are growing very modestly, thanks to these technologies’ maturity, the MRAM line is growing at a hefty 66% rate, expected to reach $44 billion by the 2032 end of the forecast window. Note that the MRAM line represents combined discrete and embedded memory.

Economies of Scale are Key

The most important determinant of any memory technology’s success is cost, and cost can only be reduced by optimizing two factors: process technology and wafer volume. The second of these is a key reason for Intel’s recent announcement that Optane was to be “wound down.”

For discrete memory chips, this fact presents a nearly impenetrable barrier that stands in the way of widespread adoption. With the help of embedded memories, this should not be as important of an issue for tomorrow’s emerging memory technology.

The economies of scale count embedded-memory wafers into the volume equation. Therefore, high-volume production of SoC and MCU wafers that include MRAM, for example, would drive down the production cost of discrete MRAM at the same time. As a result, its market could grow more quickly than without this embedded element. This process feeds upon itself, to drive the costs out of the emerging technology faster that would occur without this embedded element.

In the end, we expect to see rapid growth of an emerging memory over the next decade in both embedded and discrete forms, raising to a level that puts it in competition with today’s established technologies.