Compact RISC-V Cores Bring the Power to Wearables, Consumer Devices

Check out the other 2023 IDEA Award Nominees.

SiFive is expanding its family of high-end RISC-V CPU cores, aiming to unseat Arm’s Cortex-A series in space-constrained, performance-hungry designs such as wearables, robots, and other consumer devices.

The Santa Clara, California-based company said one of the new 64-bit cores, the P670, is its most advanced CPU yet based on the RISC-V architecture. It will compete with Arm's Cortex-A78 processor, which made it into smartphones chips for the first time in 2019. SiFive indicated that the P670 is best suited for a 5-nm process node and packs roughly the same performance as the Cortex-A78 in a 50% smaller space.

To complement it, the company also rolled out the P470 core. It features many of the same building blocks as the P670 in a more compact, less power-hungry package that will compete directly with Arm’s Cortex-A55.

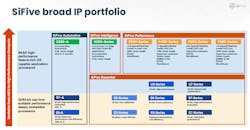

While RISC-V is an open instruction set architecture (ISA), SiFive is building a business designing a range of CPU cores and other IP (Fig. 1). Companies can buy the blueprints and assemble them into systems-on-a-chip (SoCs).

Though it’s several generations behind Arm’s Cortex-A family in terms of speed, SiFive said it’s winning in other metrics important to potential clients, such as the amount of performance its CPU core packs per square millimeter of silicon in a CPU.

“These new products offer powerful performance and compute density for companies looking to upgrade from legacy ISAs,” said SiFive VP of product Chris Jones, adding that a number of “top-tier” customers have plans to evaluate the new RISC-V cores.

The startup has raised $350 million in funding since it was founded in 2015.

Inside the IP

Where the RISC-V architecture stands out is that it’s a completely open standard. It’s supported by a wide range of companies around the world instead of being subject to the whims of a single company, like Arm.

One of the other major advantages of RISC-V is that it’s modular. Chip companies need to implement the RISC-V instruction set in their own CPU cores. But as long as they keep to the specification—which, as a reduced instruction set computer (RISC) architecture akin to the Arm ISA, consists of less than 50 instructions—a CPU will be able to run the same software as another CPU based on RISC-V.

On top of these base instructions, you can attach industry-standard (formally ratified by the companies that oversee the RISC-V standard) or even third-party extensions to adapt a CPU core for different requirements. For its part, SiFive said the P670 and P470 contain new industry-standard vector extensions that augment their ability to run machine learning and a wide range of digital-signal-processing (image, video, voice) jobs (Fig. 2).

The P670 fits in a compact, power-efficient envelope that can run at a maximum clock frequency of 3.4 GHz when fabricated on a 5-nm node, resulting in more than 12 SpecINT2k6/GHz of performance.

The 64-bit CPU core pumps out slightly less single-threaded performance than legacy solutions, aka the Arm Cortex-A78. But it can fit within a 50% smaller area on a silicon die, giving it twice the total compute density.

The P670 is based on a 4-wide out-of-order (OoO) execution pipeline that’s equipped with all of the building blocks needed by a modern processor to challenge Arm’s Cortex-A family (Fig. 3).

SiFive said it grants a 50% generational leap in performance over its previous generation, the P550. However, the amount of power it expends and performance it offers will depend on how clients choose to implement it.

It’s possible to configure the P670 in clusters of up to 16 cores, with every CPU having access to 256 or 512 kB of L2 cache memory and sharing up to 16 MB of L3 cache per core within the complex.

The P670 adds several extensions and features that bring better support for virtualization and hypervisors in hardware. Among them is a new Advanced Interrupt Architecture (AIA) compliant interrupt controller with improvements for Message Signaled Interrupts (MSI).

The company said the presence of dual 128-bit vector processing engines gives the CPU core a performance boost over its predecessor, the P650, which lacks vector compute capabilities. The P650 was previously the flagship offering in its high-performance CPU family when Electronic Design covered it last year. SiFive also claimed it was the fastest RISC-V processor IP on the market, competing head-to-head with Arm’s Cortex-A77.

The P650 is more of a general-purpose CPU core, ideal for chips that don’t require the performance that vector compute offers or are more area-constrained. SiFive is already shipping the IP to early customers.

Two CPUs in a Pod

The P470 packs many of the same extensions and features as the P670 in an even more compact package. It’s also compatible with the P670 so that you can combine the RISC-V cores in heterogeneous processors.

The startup touted the P470 as its first power-efficiency-focused CPU core for high-end wearables and other consumer electronics. Expanding on its existing P400 series and based on a 3-wide OoO execution pipeline, it offers more than double the performance of Arm’s Cortex-A55, while occupying a 30% smaller footprint when placed on a die. The result is that it delivers 4X the compute density, alleged SiFive.

Many mobile processors are based on “big.LITTLE” configurations, with large power-hungry CPU cores handling computationally heavy workloads. These cores are paired with smaller ones that focus on boosting battery life. While the P670 is designed to play the role of the high-performance compute engine in the larger heterogeneous SoC, SiFive said the P470 is better suited for the energy-efficient section.

The P470 was fine-tuned to fit in a more compact footprint and energy-efficient power envelope than the P670. But it runs at the same 3.4-GHz clock speed when manufactured on a 5-nm node, same as the P670 (Fig. 4).

Unlike the P670, the P470 incorporates a single 128-bit vector compute engine. SiFive said it also plans to roll out the P450, which will have many of the same specifications as the P470, sans the vector extensions.

According to SiFive, the P670 and P470 also are the first on the market to support the cryptography extensions in the RISC-V ISA. Moreover, they bring additional security protections with SiFive’s World Guard suite of technologies.

While RISC-V is becoming more widespread, it’s still the new architecture on the block compared to Arm and Intel’s x86. But SiFive feels that the improvements in its latest processor IP are pushing chip designers to take RISC-V more seriously.

“We are looking at possibilities of integrating SiFive’s latest products into Snapdragon platforms,” said Ziad Asghar, VP of Product Management for Snapdragon Technology and Roadmap at Qualcomm, in a statement.

The P400 and P600 families with these new CPU cores will be available in the fourth quarter of 2022.

Read more articles in the TechXchange: RISC-V: The Instruction-Set Alternative