Download this article as a .PDF

When I was involved in mainframe design, we dealt with logic gates that would be packed a few dozen per chip. Comparable designs now occur within ASICs and FPGAs. These days, designers turn to off-the-shelf, high-performance microcontrollers because they assume that FPGAs are too power-hungry, expensive, and hard to program. This is especially true for embedded FPGAs that are integrated with custom IP.

FPGA development tools and libraries have improved significantly, providing even novice designers with the ability to construct FPGA designs. Flash FPGAs provide instant-on as well as low power operation.

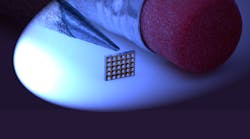

The high end of the FPGA spectrum incorporates very-high-speed SERDES and millions of lookup tables (LUT), the building block of FPGAs. At the opposite end of the spectrum are tiny FPGAs like Lattice Semiconductor’s iCE40 UltraPlus that comes in a 1.4 mm × 1.4 mm × 0.45 mm WLCSP package or conventional packages starting at 2.15-mm by 2.55-mm QFN (see figure). The flash-based FPGA has up to 5,000 LUTs, 8 DSP blocks and 1.1 Mbits of SRAM. Versions also include a MIPI-I3C interface for low-resolution, always-on camera applications. It uses under 100 µW of standby power.

The Microsemi IGLOO and Intel/Altera Max 10 are also flash-based FPGA families that come in compact packages. The Microsemi IGLOO family has up to 35K LUTs and comes in packages as small as 3-mm by 3-mm. The IGLOO/e includes a license for a soft-core Cortex-M1. The IGLOO nano uses only 2 µW. IGLOO’s Flash*Freeze mode shuts down the system while preserving SRAM and register contents. Entering and exiting this mode takes less than 1 µs.

The Max 10 is also available in a 3-mm by 3-mm package. It also has analog blocks, DSP blocks, and external DDR3 interfaces. Versions are available with up to 736 Kbytes of flash memory for soft-core NIOS II processor object code.

Xilinx’s Spartan 7 is a RAM-based FPGA that is available in an 8-mm by 8-mm CPBGA package at the low end of the family. It contains 6000 LUTs and can support a MicroBlaze soft-core processor.

FPGA Soft Core Options

Soft core processors like the ARM Cortex-M1, NIOS II, and MicroBlaze have some company these days. The RISC-V is available for FPGAs. It is possible to use the Rocket chip generator or take advantage of the PicoRV32 or Orca designs that target FPGAs.

The number of LUTs needed for a 32-bit soft-core processor vary from FPGA to FPGA, as well as between core designs and associated features like memory management units. Compact platforms fit in 600 to 700 LUTs, while higher end versions run about 2,000 to 3,000 LUTs. This is still a fraction of most FPGAs, even at the low end of the spectrum, leaving plenty of headroom for custom logic or implementing other peripherals like serial ports.

FPGA Advantages

FPGAs, even small ones, provide a number of advantages over conventional microcontrollers. FPGAs can be more flexible since they can be reprogrammed. Logic tends to be more power efficient and faster than software solutions. Designs are less prone to being copied, and some FPGA implementations go to extremes to help prevent analysis of the design.

FPGAs can also provide low-power and possibly lower-cost solutions because of the level of customization available and the efficiencies of an FGPA implementation. This is especially true where the quantity needed is insufficient to warrant an ASIC design that normally requires a significant up-front investment and large quantities to be economical.

In many cases, an FPGA approach allows single-chip solutions, whereas a microcontroller or microprocessor design would require additional chips. Electronic Design’s Embedded Revolution survey indicates that many designers are investigating deep neural networks (DNN) and artificial intelligence (AI) applications. The flexible design possible with an FPGA can support DNNs that often need only a few bits of information, allowing a small FPGA to be used while also benefitting from the parallel nature of an FPGA.