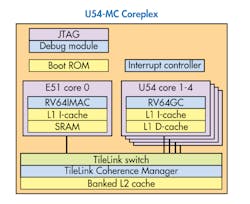

The RISC-V universe just got a little bigger with SiFive’s 1.5 GHz U54-MC Coreplex (Fig. 1). The four U54 cores implement RV64GC that includes support for hardware multiple and divide, atomic instructions, 16-bit compressed instructions, and single and double precision floating point support. These cores include user (U), supervisor (S), and machine (M) privilege modes. Operating systems such as Linux are supported.

The U54 cores support virtual machines (VM). “The hardware will support running hypervisors designed for the hypervisor mode, but because we do not actually implement the hypervisor mode in hardware, some of the functionality is emulated in low-level software,” said Andrew Waterman, co-founder and chief engineer at SiFive. “So, while it will be software-compatible with the hypervisor mode, the performance will be lower than a full hardware implementation of the hypervisor mode.” Of course, most applications will not require VM support.

The E51, or “minion core,” implements the RV64IMAC architecture. This foregoes the floating point and virtual machine support. It only needs the user (U) and machine (M) privilege modes since it is designed for peripheral management. It can be used while the quad core complex is powered down to reduce power requirements while tracking devices like 9-axis sensors.

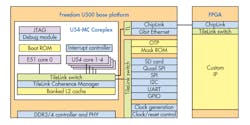

The cores share a 2 Mbyte, 16-way, L2 cache. This is tied to a DDR3/4 controller in the Freedom U500 base platform that includes peripherals, along with an optional high-speed serial ChipLink interface that allows U500 to be paired with an external high-speed device like an FPGA (Fig. 2).

The Freedom U500 base platform fits into a 30 mm2 die using TSMC’s 28 nm process. This is about 250 million transistors. The processors and L2 cache all have ECC support.

The RISC-V instruction set architecture (ISA) is actually designed to deliver compact code size in addition to high performance. SiFive’s microarchitecture implementation is designed to improve on this. The U54 core delivers 1.7 DMIPS/MHz and 2.75 CoreMarks/MHz. It can be clocked up to 2.6 GHz, although it is typically run at 1.5 GHz.

The platform is supported by the GCC toolchain and LLVM support has been submitted for inclusion in the standard LLVM tool chain. Linux support with glibc is targeted for February 2018. The system is supported by the Eclipse-based Freedom Studio that runs on Windows, Linux, and MacOS. The chip will work with JTAG emulators like Segger’s J-Link Probe. Development boards will be available from SiFive in 2018. The soft IP version of the U54-MC Coreplex system is available now.

RISC-V is still a relative newcomer, but it now spans a significantly wider application space. While the Freedom U500 may not challenge the high-end platforms found in the latest smartphones, it easily takes on midrange platforms as well as embedded applications that need multicore performance.