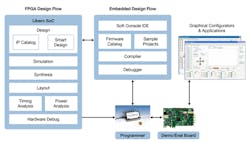

A longtime supporter of the RISC-V (pronounced RISC Five) instruction set architecture (ISA), Microsemi provides tools and RISC-V soft cores for its various FPGA lines, including the recently unveiled Mi-V (pronounce My Five) ecosystem. Mi-V further streamlines RISC-V development by giving software developers a starting point that’s able to bypass the FPGA design process, while offering FPGA developers an easier starting point for RISC-V-based designs (Fig. 1).

The Mi-V ecosystem includes the Libero SoC IDE and the Soft Console IDE. The former is the FPGA design tool. The latter is an Eclipse-based IDE for software development. It comes with the RISC-V toolset, so it’s only a matter of software developers utilizing it. Of course, generating a custom FPGA configuration will require use of the Libero SoC.

1. The Mi-V development environment for RISC-V includes the Libero SoC IDE for FPGA design and the Soft Console IDE for software development.

I have tried out SiFive’s HFive1, which is a hard-core RISC-V microcontroller. Using it for development is on par with most other microcontroller and microprocessor platforms. The only difference was the RISC-V target.

Getting started with Mi-V is on par with the HFive1 experience that allows software developers to get up and running quickly without needing to deal with the complexities of an FPGA. This is done by providing predefined configurations. The Microsemi platforms actually have an advantage of being able to utilize the FPGA’s flash memory for code and data, enabling a self-contained platform. It also allows for a secure-boot implementation. In addition, Mi-V includes CoreBootStrap support.

Mi-V supports a range of Microsemi development platforms, such as the IGLOO2-based Creative Board (Fig. 2). This board incorporates sockets for three popular interfaces, including PMOD, MikroBus, and Arduino Shields. The Creative Board has a RISC-V platform and peripherals available so that software developers can start programming almost immediately.

2. Microsemi’s Creative Board integrates an IGLOO2 FPGA that easily handles a RISC-V soft core. The board also has sockets for PMOD, MikroBus, and Arduino Shields.

The Mi-V ecosystem is actually more than a preconfigured RISC-V soft-core implementation plus the FPGA and software development tools. It includes a version-controlled, firmware catalog of drivers for matching FPGA IP. These drivers are MISRA- and QNX Neutrino-compliant.

Probably more important is the RTOS support, which offers open-source and third-party options. The open-source options include FreeRTOS, Huawei LiteOS, and Apache’s MyNewt. Third-party options are ExpressLogic’s ThreadX and Silicon Labs Micrium µC/OSIII.

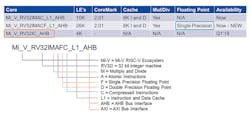

Developers have access to three cores (Fig. 3). One of them features single precision floating-point support. None support the RISC-V user-mode option as of yet. The Mi_V_RV32IC_AHB is a small soft core that uses about 4K LEs, including debug support. The Mi_VRV32IMAC core can deliver 2.01 EMMBC CoreMarks/MHz that bests the soft competition.

3. The Mi-V environment initially supports three RISC-V configurations.

Mi-V represents a major step forward for RISC-V. RISC-V’s open nature makes it interesting for applications such as military and avionics, where the open-source RTL can potentially make certification easier.

It is possible to generate new RISC-V soft cores using tools like the open source Rocket Chip Generator. The advantage of using the Mi-V cores is that they are already configured and verified.