Safety-Aware Chips Serve Automonous-Driving Apps

Check out more TechXchange Talks videos.

Advanced driver-assistance systems (ADAS) and self-driving vehicles utilize lots of computing power, which needs to be able to meet standards such as ASIL B and ASIL D. Arm has been designing chips to meet these stringent standards so that developers can deliver safe and reliable vehicles.

I talked with Arm's Robert Day, Director, Autonomous Vehicles, and Tom Conway, Director, Product Management, Automotive, about the designs and issues associated with these type of chip designs (see the video above). This includes the use of techniques like lockstep processors.

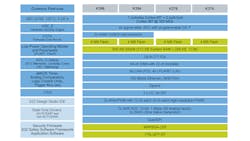

Arm starts its lockstep designs with the Cortex-R family, but it has been expanded to include the Cortex-M and Cortex-A families. As a result, developers can choose the most appropriate platform and combination, such as NXP's S32K39 that includes two pairs of 320-MHz Cortex-M7s (see figure).

The S23K39 employs a DMA that also runs in lockstep mode. Thus, each operation is checked to make sure the redundant operations are identical. Designers typically employ Arm cores along with other safety and reliability features like error-correction-code (ECC) memory.