Bridgeless PFC Boosts Low-Line Efficiency

Wide input-voltage range power factor correction (PFC) converters present some of the most difficult component challenges in ac-dc power electronics. With an input-voltage range that can extend from 265 Vac to as low as 75 Vac, the range of operating conditions is relatively extreme with wide current operating range and duty-cycle demands. As energy costs soar, the pressure is on to find ways to improve efficiency in power supplies used for applications such as telecommunications and computing. One solution is the bridgeless PFC technique.

Bridgeless boost PFC is a concept that has been long on promise for many years, but has not reached mainstream acceptance. Issues with EMI, robustness and the complexity of early configurations have stymied efforts to realize the bridgeless boost PFC converter's potential. Furthermore, improvements in components used in standard PFC boost converters have resulted in efficiency gains that did not justify the extra cost and complexity of the bridgeless configuration. And while bridgeless PFC has been viewed as a potentially useful technique to improve low-line input efficiency, it is not certain that is where the demand for improvement lies today.

As discussed in many forums over the last two years, the specification and evaluation of switch-mode power-supply (SMPS) systems is changing in response to the industry's desire to save energy in the real world. Traditionally, efficiency has normally been specified at full load for high- and low-line ranges, but now a more realistic approach is being widely adopted, looking at the behavior of the system and its efficiency in the range where the SMPS usually operates.[1] This means that for redundant power systems such as computing servers and telecom power, it is now realized that efficiency in the 10% to 50% range must be considered along with full load behavior, as shown in Fig. 1.

As a result, system manufacturers such as IBM are changing the focus of how they specify and procure power. This change has been driven by customers with limited abilities to expand data centers because of power and cooling capacity. While the best of contemporary conventional PFC designs can just meet such current voluntary standards as Green Grid and ClimateSavers, more stringent future requirements may force designers to look for new solutions. A bridgeless PFC input configuration can help support these requirements, although it may require some rethinking of design methodology and optimization methods.

Conventional PFC Versus Bridgeless

The well-known single-boost PFC rectifier configuration shown in Fig. 2a consists of a full-bridge rectifier input, which provides a rectified pulsating half-sine waveform applied to a boost converter consisting of switch S1, boost inductor L1 and boost rectifier D1, which charges a bulk rectifier capacitor, “bus cap.”

Fig. 2b shows the basic bridgeless boost concept, patented in 1983.[2] This variant shows a dual-winding inductor on one core. With alternating half-sine polarity on the ac line voltage, the MOSFETs alternate between operating as a low-frequency half-wave rectifier diode connecting the ac line voltage to the bulk bus negative terminal. It also operates as a high-frequency chopper driving the respective boost inductor winding and boost rectifier diode.

This configuration reduces the number of semiconductor devices in the inductor charging-current path from three to two, lowering conduction loss by about one diode-junction voltage drop (VF ). The MOSFETs conduct as either a high-frequency switch or a low-frequency half-wave rectifier operating on alternate ac half cycles. As a result, some of the power losses normally handled by the ac bridge rectifier are now transferred to the power MOSFETs, potentially resulting in higher junction temperatures, which affects the overall MOSFET size.

Deterring the industry's adoption of the bridgeless PFC are several innate configuration characteristics. Because of the inductor configuration and lack of a low-frequency path to the output, there is a relatively high common-mode switching voltage present at the bulk negative connection and no low-frequency path to the ac input. This can result in relatively high common-mode EMI because of the charge and discharge of normal parasitic capacitances associated with the converter's physical construction.

Sensing the input voltage and input current usually require isolated circuits due to the high-frequency potential between the ac input and output ground reference. It may even be necessary to use dual current-sense transformers (for switch and inductor current), while also applying rectified half-sine voltage sensing on the primary.[3] This example makes no provision for precharging the bulk capacitance or dealing with surge stress encountered during cycle skip or low-line to high-line jumps.

Hall Effect Current Sensing

A modified version of this configuration was used to develop an experimental high-efficiency bridgeless PFC front end in coordination with Isle Engineering, an independent consulting company in Ilmenau, Thuringia, Germany, up to a maximum output power level of 1500 W.[4]Fig. 3 shows the basic configuration. Some of the design issues for this bridgeless PFC were addressed with specific techniques to optimize efficiency to the greatest extent possible, with a target value of 99% at full load. In practice, these efforts made it possible to realize about 98.8% efficiency at full output in the finished design.

First, input-voltage sensing was eliminated by using a PFC controller based on single-cycle control, as pioneered by Smedly and Cuk.[5] This does not require input-voltage sensing and PFC controllers are available from vendors that use this technique.[6] The LAH25 wideband Hall Effect sensor with isolated data outputs accomplishes current sensing on the ac primary after the bulk precharge diodes D3 and D4. This component avoids the losses associated with resistive sensing and eliminates the need for sensing transformers in high-speed switching paths.

The boost rectifier diodes are silicon carbide, merged PiN Schottky types that combine the characteristics of Schottky and p-n diodes with nearly negligible reverse recovery charge (QRR) capacitive losses and low forward drop. The switching MOSFETs were selected for low-energy-specified output capacitance (COSS) to minimize turn-on loss and are capable of near zero-voltage switching turn-off with very low losses due to their output capacitance nonlinearity.[7]

The control arrangements for this configuration are somewhat complex, and a zero-crossing detector and driver-steering logic located after the PWM output of the PFC controller steer the driver signal to either S1 or S2. This depends on the ac-voltage input phase while driving the other MOSFET as a synchronous rectifier. A flyback bias supply, using an integrated controller and FET, provides ±12 V for the PFC controller and Hall Effect sensor module, which is part of the overall losses accounted for in the efficiency measurement.

This development was successful in demonstrating a range of techniques to achieve quite high efficiency in the PFC front end, but it was limited to a high-line configuration due to the lack of conventional heatsinks, and suffers from the common-mode EMI issues of the original configuration. Derivations of another proposed configuration address these issues.

Half-Wave Design

A bridgeless half-wave rectified dual boost PFC was proposed by Barbi and Souza that used insulated-gate bipolar transistors (IGBTs) with a nondissipative snubber to reduce switching losses.[8] IGBTs lack the functional body diode of MOSFETs, so diodes must accomplish input half-wave rectification (slow-recovery diodes are sufficient). A modification of this design was adapted to MOSFETs, removing the nondissipative snubbers and adding diodes for bulk capacitor precharge (Fig. 4).

Diodes D5 and D6 are low-frequency half-wave rectifiers, alternately making a low-frequency connection between the ac line and the bulk negative connection. Diodes D3 and D4 provide the bulk precharge function during startup and in cycle skip or brownout recovery. The configuration of D3, D4, D5 and D6 forms a bridge and can be implemented with standard slow-recovery ac bridge rectifiers.

Chopper switches S1 and S2 drive inductors L1 and L2 on alternate line half cycles. This is a potential cost disadvantage compared with the combined coupled-inductor structure of the last example. However, by using separate cores high-frequency excitation and heating occurs for each inductor only during every other ac half cycle, providing thermal benefits that reduce inductor size and cost. Some half-wave rectification still occurs through the inductor and the MOSFET body diode, shown in Fig. 4, because they're not the primary half-wave rectifier used for other configurations.

The majority of current flows in diodes D5 and D6, slow-recovery half-wave rectifiers. This has the effect of reducing the power dissipation and maximum junction temperature in the MOSFET switches, which lowers their effective operating on-resistance (RDSON). MOSFET RDSON can double between room temperature and maximum operating temperatures, so a lower junction temperature lowers conduction losses.

In this configuration, current sense is at the same potential as the output load return and controller ground, allowing some flexibility in measurement technique and including the use of conventional resistive in-line sensing. Of course, resistive sensing increases the losses, but by how much?

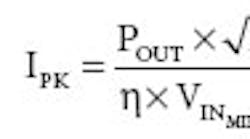

Let's consider an example of a 1-kW output converter, assuming a nominal efficiency (η) of 90% and a low-input-line voltage of 90 Vac. Let's assume that for the controller being used, we need 26 mΩ to generate the required maximum sense voltage. The peak input current is:

The sense resistor power dissipation is:

This amounts to 0.5% efficiency loss at low line. However, if normal operation at high line and cost are a greater concern, at 208 Vac the total PSENSE loss is only 0.755 W, less than 0.1%. This may be a tolerable tradeoff. Note that eliminating the extra diode drop of the conventional bridge diode even at high line may save 5 W to 8 W.

Examining this bridgeless PFC configuration, it could appear that the component count is double that of the conventional PFC configuration in Fig. 2a. In reality, with the same total MOSFET and boost rectifier silicon “budget” in either configuration, a higher total efficiency can be achieved with the bridgeless configuration. And considering the targets shown in Fig. 1, achieving higher efficiency at the lower power ranges is well served by splitting up the switch and diode budget between the dual boost phases.

To understand why this is so, examine the selection of the MOSFETs based on a conventional boost PFC that delivers the lowest total losses at full load and low-line ac. An Excel workbook was used to do this, with some assumptions translated from the data sheet to the application (Fig. 5a).

Fig. 5 shows an 800-W output PFC application, with a net input to output efficiency of 85%, which is used to factor up the required input power. The switching frequency is 130 kHz, with an input voltage of either 90 Vac in Fig. 5a or 208 Vac in Fig. 5b. The x axis is the nominal RDSON specification, but this is not used for calculation; instead, the RDSON is normalized to 105°C for the calculation of conduction losses.

Since turn-off losses can be made nearly negligible with super-junction MOSFETs[7], the focus for dynamic losses is on COSS discharge at turn-on, an unavoidable loss in hard-switching circuits. With conventional diodes, this loss might be nearly swamped out by the QRR and COSS of the boost rectifier diode. With modern silicon carbide and even silicon ultrafast diodes, the output capacitance of the MOSFETs can play a dominant role in losses.[9]

Looking at Fig. 5a, the minimum of the loss curve occurs for a specified RDSON of 25 mΩ to 30 mΩ. At this point, at full load and low line, the conduction and switching losses are balanced and minimized. This low resistance would take two 75-mΩ TO-247 MOSFETs in parallel to achieve. This may not be the best way to achieve efficiency, particularly if we consider the bridgeless option. Those switching losses due to COSS capacitance will be there regardless of the load current or line voltage.

Considering that the bridgeless option can save 5 W to 8 W or more in conduction losses, we can take that savings into account in derating the conduction performance requirement for the MOSFETs. Moving on the loss line to the right, the losses increase as a function of conduction loss, so it's possible to move over to the right, where conduction losses are up by 5 W to 7 W, and write that off due to the conduction loss improvement of the bridgeless configuration.

Most importantly, shifting to a single 75-mΩ, instead of a 25-mΩ to 30-mΩ MOSFET cuts COSS switching losses in half. Therefore, switching loss reduction at all other load ranges and line voltages will be significant. This is shown in Fig. 5b for operation at full load at the SMPS normal operating 208-Vac input, where the optimum MOSFET choice would appear to be around 100-mΩ. In fact, if you have that so-called “optimum” conventional MOSFET of 25 mΩ to 30 mΩ for low-line performance in a conventional PFC circuit, the total losses at full load are doubled for the MOSFET, due to higher COSS switching loss when operating at 208 Vac. The loss is even worse at 50% load and below.

References

-

Janick, J., “IBM Technology and Solutions,” IBM Power and Cooling Symposium, October 2007, Raleigh, N.C., proceedings at www-03.ibm.com/procurement.

-

Mitchell, D.M., “AC-DC Converter Having an Improved Power Factor,” U.S. Patent 4,412,277, Oct. 25, 1983.

-

Moriconi, U., “A Bridgeless PFC Configuration Based on L4981 PFC Controller,” Application Note AN 1606, STMicroelectronics, November 2002.

-

Hancock, J., “Meeting the Challenge for Offline SMPS Through Improved Semiconductor Current Density,” IBM Power and Cooling Symposium, 2005, proceedings at www-03.ibm.com/procurement.

-

Smith, K.M., Jr.; Lai, Z.; and Smedley, K.M., “A New PWM Controller with One-Cycle response,” IEEE Transactions on Power Electronics, Volume 14, Issue 1, January 1999, pp. 142-150.

-

Lu, B.; Brown, R.; and Soldano, M., “Bridgeless PFC Implementation Using One Cycle Control Technique,” IEEE Applied Power Electronics Conference (APEC) 2005 proceedings, pp. 812-817.

-

Bjoerk, F.; Hancock, J.; and Deboy, G., “CoolMOS CP: How to Make Most Beneficial Use of the Latest Generation of Super Junction Technology Devices,” AN-CoolMOS CP-01, www.infineon.com.

-

Souza, A.F., and Barbi, I., “High Power Factor Rectifier with Reduced Conduction and Commutation Losses,'' International Telecommunication Energy Conference (INTELEC) proceedings, June 1999, session 8, paper 1.

-

Lu, B.; Dong, W.; Shao, Q.; and Lee, F., “Performance Evaluation of CoolMOS and SiC Diode for Single Phase Power Factor Correction Applications,” IEEE APEC 2003 proceedings.