Build a Better, Faster, and Stronger Power Supervisor

Rapid growth of FPGA- and DSP-based systems has increased the need for enhanced power supervision ICs. These systems include applications ranging from telecommunication switches and networking routers, to industrial automation and medical test equipment, requiring more than $500 million of power supervision ICs to be sold each year. Not only the quantity of these applications increases, the complexity of such systems grows as well. Next-generation systems contain multiple FPGAs, ASICs, DSPs, microcontrollers, and other miscellaneous ICs, each of which can require multiple and different voltage rails to function. It is common to see systems contain 8 or 10 voltage rails and up to 16 voltage rails in some applications. Certain applications have even been known to exceed 20 voltage rails.

Applications that use power supervision have the requirement to uphold the upmost reliability. System power must work flawlessly at all times, and power rails must be ramped up and down in the proper sequence with appropriate delay times. They must constantly monitor irregular activity and detect faults pertaining to voltage and current. They must also have the ability to recover from faults. A typical power supervision system is reflected in the block diagram shown in Fig. 1.

Fig. 1.Dedicated IC Power Supervision Block Diagram.

When developing a power supervisor for today’s demanding applications, there are three primary challenges that system engineers face. These challenges can often cause companies to waste one of their most valuable resources: time.

• Challenge 1: Newer low-voltage power rails demand greater accuracy. Modern FPGAs and DSPs require voltage rails of 1V and lower. This requires power supervisor systems to contain 0.5% (5 mV) or better measurement/monitoring accuracy and contain 1.0% (10 ZmV) or better trimming accuracy. Meeting both of these needs requires more expensive analog ICs to achieve this level of accuracy. Being able to accurately measure and control the voltage of each rail is essential to ensuring the overall reliability and stability of the system.

• Challenge 2: The number of power rails is increasing. As mentioned, it is not uncommon to see a minimum 8 to 10 rails, but with some newer systems require more than 20 power rails. This exceeds the monitoring capabilities of many off-the-shelf power supervisor ICs. This causes the need to chain together multiple power supervisor ICs to monitor all voltage rails in a system. The greatest disadvantage to doing this is that adding even more ICs to a system equates to more potential Points of Failures (PoFs).

• Challenge 3: Each power supervisor board often requires complex customization. Traditional off-the-shelf power supervisor ICs do not have the flexibility to create a universal architecture that can be shared across multiple systems. Each system may have a different number of power rails, voltage sequencing order, power monitoring requirements, or voltage trimming needs. These design differences can increase development cost and time-to-market. Each time a new system is developed, design must begin at square one, beginning with selecting a new power supervisor IC.

DEDICATED IC APPROACH

Using a dedicated power supervisor has been the traditional approach for many applications. The advantage to using dedicated power supervisor ICs is that some of them can be directly powered off a higher voltage rail such as 12 V rather than requiring a lower voltage auxiliary power rail. There is also a wide variety of selection available on the market when it comes to selecting a power supervisor IC. Some power supervisor ICs even have a built-in charge pump circuit, high-voltage FET drive output, integrated voltage attenuation networks, and dedicated DACs for each trim output rather than require a PWM with a low pass filter.

While dedicated ICs can overcome many of the challenges mentioned earlier and provide an adequate solution for some applications, system engineers are discovering this not to be the case in newer and more advanced systems. Of the three design challenges listed earlier, the primary challenge faced by power supervision ICs is the limitation of rail monitoring capacity. Many devices can only handle management of 8 to 12 voltage rails, which includes voltage sequencing, voltage/current monitoring, and voltage/current fault detection. Any more than this requires multiple power management devices. Additionally, on top of needing one or more power supervisor ICs, additional devices may also be required, such as current sense amplifiers (CSAs) for current measurements and external EEPROMs for fault management. This introduces additional cost and potential points of failure to a system.

THE SYSTEM-ON-CHIP (SOC) APPROACH

An alternative approach to using a dedicated power supervisor IC is to utilize a System-on-Chip device with mixed-signal functionality. This functionality allows for a soft-core CPU to be surrounded by various analog and digital peripherals that are configurable. Thus, the SoC can be tailored for a specific application while not being locked into a configuration solely and specifically for a single application. SoCs allow developers to integrate $10+ of power supervisor ICs and other miscellaneous devices onto a single chip by incorporating an entire power supervisor system into a single SoC device as shown in Fig. 2.

Fig. 2. System-on-Chip Approach to Power Supervision.

This figure demonstrates how 16 voltage rails can be implemented into a single device to exceed the capabilities of traditional power supervisor ICs.

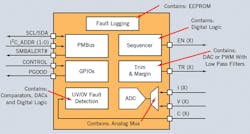

Another consideration is what peripherals are required to implement a power supervisor system. To answer this, refer back to the block diagram of a power supervisor shown in Fig. 1. The individual system components can be analyzed to understand the requirements on a silicon level. An annotated version of the power supervisor block diagram is shown in Fig. 3, which provides a list of the peripherals used in creating a power supervisor system.

Fig. 3. Required Peripherals of a Power Supervisor.

As shown in Fig. 3, the primary components required are an ADC, some analog multiplexers, comparators, DACs, EEPROM, and some configurable digital logic. These are all peripherals that can be found in mixed-signal SoC devices. Some SoC devices can integrate more than others; capacity and flexibility is dependent upon internal device routing and configuration. Having these capabilities allows for additional integration and repurposing of device resources via Dynamic Reconfiguration, which allows for the configuration of a device to be altered dynamically during run-time.

Using the mixed-signal architecture of an SoC, an entire Power Monitoring solution can be created using specific programmable digital and analog peripherals, as shown in Fig. 4.

Fig. 4.Using Programmable Analog and Digital for Power Supervision.

This approach also has the benefit of scaling accordingly to different system requirements. Using a single device, system engineers can change the number of rails or sequencing configuration, with minimal adjustment, without having to change the core configuration and layout.

In addition, many features such as multiple PMBus interfaces and EEPROM fault logging can be added or removed from the same device across multiple designs. SoC devices, such as PSoC from Cypress, enable a single-chip design for power supervision by integrating the capabilities of an ASIC, configuration benefits of a dedicated IC, and the price point of an embedded microcontroller.

SoC devices can also improve the overall reliability and safety of a power supervision system. Since the entire power supervision system is integrated into a single device, self-testing can be performed on the device in a straightforward and reliable manner. In the event that a fault does occur, onboard EEPROM can be used to store an array of detailed fault information such as the fault type, what rail the fault occurred on, the last several ADC readings for each rail, status of various IO, and a time stamp of at what point in time a fault occurred.

Because of their flexibility, SoC devices are not fixed in functionality as are other dedicated ICs. For example, in some systems, such as networking switches and routers, thermal management is required in order to measure temperature within a chassis, via and RTD or diode, and adjust fan speed accordingly to properly cool the system. This traditionally requires additional external ICs in order to implement this functionality. SoC devices allow for both power and thermal management to be implemented in a single device to reduce overall cost and increase reliability. Fig. 5 shows how the same SoC device used for only power supervision can be expanded into an all-inclusive system supporting thermal management as well.

Fig. 5. Using Programmable Analog and Digital for System Management.

An example of SoC devices that are capable of achieving the described functionality are the Cypress Semiconductor PSoC family of devices. The PSoC device family includes: programmable analog routing, functional blocks for analog peripherals, PLD logic to create digital peripherals, and a multitude of device cores. Fig. 6 shows a block diagram of a PSoC 3 and PSoC 5LP, along with it’s mixed signal components that are used to create a power supervisor solution.

Fig. 6. Block Diagram of PSoC Device.

Fig. 7. Implementing Power Supervision in PSoC using PSoC Creator.

Each portion of a power supervisor, such as Trim or Sequencer, is broken up into what are called “components” in PSoC Creator. The PSoC Creator software allows developers to place individual components on a visual schematic that correspond to specific power supervisor functionality.