FPGA-Based Design for Low System Power Consumption

Today, system designers are compelled to design systems optimized for minimum power, particularly with FPGAs. To minimize FPGA power consumption, we should look at its total power consumption, which is primarily:

- Inrush/Power-up current

- Configuration

- Static current

- Dynamic current

Now, we should look in detail at each power consumption factor:

Inrush/Power-up current—When an FPGA powers up, it needs to establish internal biases and complete reset sequence. It causes a current surge that may generate a spike as high as several amperes for as long as a few hundred microseconds, resulting in an In-rush power. This power component is de-emphasized by FPGA vendors, but can play a major role in impacting power supply design and hence impacting the overall system cost and real-estate requirements. Power-up current does not impact total power to a large extent in applications where system does not go through power-cycle frequently. However, in applications where a frequent power-cycle is needed, power-up current itself is a power-hog.

Apart from total power consumption, instantaneous power consumption is the challenge imposed by power-up current. Power-up current is several times higher than the operating current of FPGA that needs supply specifically designed to deliver current needed at power-up. Additionally, SRAM-based FPGAs need power sequencing, and not following the sequencing can cause power-up current to be much higher than what is mentioned in device datasheets. This further adds the need of a power sequencing circuit and hence additional cost and real-estate requirements.

Considering all these factors, it is of utmost importance to understand the power-up current specification of the FPGA before selecting it for any system. Flash-based FPGAs have a significant advantage for low-power design with no in-rush current spike, simplified POR (Power ON Reset) sequencing, and lower overall power supply cost.

Configuration Current—SRAM-based FPGAs do not retain configuration when power is lost; they need to reload configuration data from external non-volatile memory at power-up. This consumes significant current for several hundred msec and can result in shorter battery life for systems with frequent power cycling. Flash-based FPGAs retain configuration on power down and therefore do not use any configuration current.

Static Current—Static current consumption is also called quiescent current. It is the result of leakage in the transistors. Static power consumption becomes very important for total system power consumption as it is the constant power that will be consumed by the device as long as it is powered (if low-power modes are not available). Static power is not dependent on the switching frequency and hence needs to be examined carefully in applications where the system runs on a low operating frequency, resulting in lower dynamic power. In such designs, static power will dominate the overall power consumption numbers.

SRAM-based FPGAs are composed of SRAM cells with six transistors per cell, with multiple leakage paths, resulting in substantial leakage current per cell and high static current for the device. In comparison, Flash-based FPGAs consist of just one transistor with 1000x lower leakage current per cell resulting in ultra-low static power.

Dynamic Current—Dynamic FPGA power consumption is:

P = CV2F (1)

Where:

P = Dynamic power in watts

V= Operating voltage in volts

F= Frequency in kHz

C= Load capacitance in µF

Higher operating frequency results in higher dynamic power consumption. All FPGA vendors provide estimators to estimate the dynamic power based on the resource utilization and switching frequency. It is important to do power estimation before selecting a device for the system.

All power components that are discussed contribute toward the total power. When a device powers up, power-up current contributes toward the total system power consumption that can be of the order of several hundred mA or several Ampere in higher density FPGAs. While the system is powered on, static and dynamic power take over the power budget.

From system perspective, thermal management also becomes a challenge when average power consumption is high. In such a scenario, if thermal management is not accounted for, it can cause thermal run-away.

Impact of Design Requirements on Power

For systems where uptime is almost 100%, that is most server applications, static and dynamic power will be the most important to examine; however, if the device is operating at a higher frequency, the total power is dominated by the dynamic power consumption of the device.

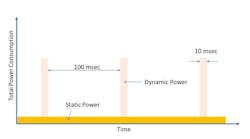

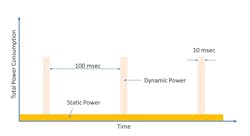

In contrast, let us take an example of a remote sensor node that needs to capture some data, process it, and transmit to the host device. In such applications, logic does not need to switch all the time because the device can sample data, process it, transmit and then the clock to the logic can be gated to avoid any switching until another sample needs to be processed. Figure 1 shows the power profiling of such a system, where active time needs to be about 10 msec and then sleep time for about 100 msec.

In such applications, static power is the primary factor contributing to the total system power. Hence, it is mandatory in such applications to pick a device that consumes low static power. Another thing to consider here is the operation at a lower frequency and not go for burst mode. System design analyses both the scenarios and picks one that works best for the system.

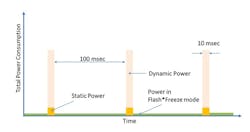

Low power modes can help in further reducing the FPGA’s power consumption. Low-power modes, i.e., sleep, deep-sleep, and so on are well known in microcontroller devices. Similarly, some FPGAs also support some form of low-power mode that is useful in applications where low-duty cycle operation is needed. Usability of these modes depends on factors like power saved in low power mode, transition time from one power mode to another, design complexity, and so on. SRAM-based FPGAs need device reconfiguration when they come out of low-power mode that results in long exit time. It causes current surge at the time of reconfiguration. Also, register data is lost during down time. However, these modes should be examined as they are useful in some applications. Some of the flash-based FPGAs (i.e., IGLOO, IGLOO2, and SmartFusion2) support Flash*Freeze mode, which allows a device to enter ultra-low power mode while retaining SRAM content, I/O state, and register data. Depending on the device family, Flash*Freeze mode can be exited using various sources like I/O activity, I/O signature match, or RTC wakeup interrupt. Also, no external clock is needed for RTC time-keeping. In Flash*Freeze mode, internal clocking circuits are powered down. Entry and exit times are almost negligible as only time that is needed for exit is primarily the PLL lock time when it is powered up and that is <100 µsec. Figure 2 shows what power profiling looks like when Flash*Freeze mode is used. However, it does not consider entry and exit time as it is negligible in flash-based FPGAs.

Input/Output Pin Power Consumption—Input/Output pins are major power consumers. I/O power consumption depends on load, slew rate and drive strength. A device that supports configurable slew rate and drive strength can significantly help in reducing total system power. The availability of low-voltage I/O standards can also help in power reduction.

Hard IP—Hard IP (Intellectual Property) is optimized in terms of power and real estate requirements. There are some IPs those are commonly used in applications (i.e.,communication interfaces like UART, I2C, SPI, DDR controllers, serial transceivers or SERDES, PCIe, and so on). Based on the application, it is good to find a device that has Hard IP and each IP’s power should be analysed while comparing two devices. For example—SERDES can consume a lot of power if used in an application. Some FPGAs have low-power SERDES transceivers such as SmartFusion2 and IGLOO2 devices, which are optimized for power and consume up to 5x lower power compared to other FPGAs

With regard to hard IPs, it is also important to understand the actual system requirements that can help in selecting a device that has only the required hard IPs and ensures that you do not pay for features that you do not need and keep current consumption requirements as low as possible. One of the best examples is high-end application processors available on some FPGAs. Though these processors are useful in calculation-intensive applications, they add huge static power if they are used for a short time or operated at a lower frequency. For example, SoC devices with A9 processor core add up to 700 mA static current over the supported temperature range.

Designing for Low Power

Software development tools can significantly impact product development life cycle when designing for low power. If development tools have features to estimate the power consumption, provide user friendly options to optimize total power, and easy access to low-power modes offered by silicon, it makes a system designer’s life easier and reduces development time that is essential in today’s competitive market.

Almost every major FPGA vendor supports power estimation feature as part of development tool. For example, the SmartPower tool from Microsemi provides a detailed and accurate way to analyze designs. The tool provides top-level summaries as well as power consumed by lower-level specific functions within the design, such as gates, nets, I/Os, memories, clock domains, blocks, and power-supply rails.

To design a system for low-power consumption, it is important to select devices that are designed to operate at low power. Power-up current, configuration current, static current, and dynamic current must be examined independently and power profiling must be done to understand the impact of each of these power components on total system power. Flash-based FPGAs have an inherent advantage over SRAM-based FPGAs in terms of power consumption. Low-power modes are useful and can provide a lot of power saving in application where system does not need to be in active state 100% of the time. A device with rich Hard IPs is useful in further reducing static and dynamic power. Development tools, which have features and capabilities to enable low-power system design, can help in implementing a power-efficient system at a lower development cost and reduced time-to-market.