Get the Most Out of Ultra-Low-Power Modes to Boost Wearable Battery Life

Portable and wearable electronics are on the rise in personal and business use, as evidenced by the increase in available products. Also, medical devices traditionally used in hospitals and clinics are evolving to become more portable, creating new possibilities for their use in the home healthcare market.

These wearables are battery-operated and embedded with sensors, actuators, and internet connectivity, which enables these devices to interact with other devices over the internet as well as be remotely monitored, analyzed, and controlled. Such devices must continuously capture and log an increasing amount of user and sensor data while using as little power as possible.

Often these systems have restricted form factors, requiring all of the electronics and associated accessories to fit in a confined space. This also restricts the space for attaching batteries, limiting battery capacity and operating life. Smaller batteries need to be recharged more often, which is highly undesirable, especially for wearable medical devices that serve a vital function. Improving a system’s battery life usually comes down to the following two options:

- Reduce the system’s active current consumption and active time

- Reduce low-power leakage currents when the system is either in standby mode or sleep/hibernate mode

One area where engineers can maximize their optimization efforts to reduce power is by making the most of the ultra-low-power modes available with memories designed for the portable and wearables market. Extremely low active and standby currents, combined with peak (Inrush) current control, enables engineers to not only reduce total system power but also keep the system’s total peak current lower. Low peak-current control during power-mode transitions plays an important role in optimizing total system energy consumption. It also improves battery reliability over time by protecting it from being overdriven.

Reliability Issues Associated with Battery Overdrive in Wearables

Li-ion batteries have become de facto choice for many portable and wearable electronics for many reasons compared to other battery technologies. These include higher energy density, higher energy efficiency, higher operational voltage, lower leakage (self-discharge), lower weight, and lower maintenance with a moderate charge/discharge cycle life.

However, even though Li-ion batteries have excellent characteristics to support portable systems, they pose serious challenges due to their sensitivity to overcurrent drawing, overcharging and discharging, short circuiting, and thermal instability. These sensitivities in LIBs can lead to catastrophic system failures if not carefully addressed through the overall system design. Further complicating the issue is that there’s no specific or best approach to mitigate these issues. As a result, different OEMs take different approaches to ensure systems with these batteries always operate within their safe limits.

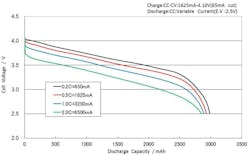

As can be seen in Figure 1, drawing higher current from Li-ion batteries produces a lower output voltage. This in turn can cause systems to become more susceptible to power failure even with minor voltage fluctuations. Hence, to protect against such failures, systems must keep their total current consumption below a prescribed threshold. This is possible to achieve either by increasing battery capacity (mAh) or by specifically designing the system with ultra-low-power components to keep the total current with acceptable limits.

For wearables and portable systems, increasing battery capacity is typically not an option. Therefore, engineers must pay particular attention to total current consumption.

Addressing Current Surge During System Bootup

One way to enhance system battery life is to have a highly optimized duty cycle. In such a cycle, the system wakes up periodically for a very short duration, completes its defined tasks, and then goes back to an ultra-low-power mode such as sleep or hibernate mode. However, when systems start up from an ultra-low-power mode, the peak/inrush current surges due to system core and peripheral components powering up simultaneously.

To compensate for such current surges, systems can stage their bootup sequence by adding extra circuits and firmware logic to limit the peak current demand during the bootup event. This approach comes at the cost of delayed system readiness, which can compromise system performance both in terms of device functionality and user experience.

An alternative to staged bootup is controlling the peak current in individual devices. However, this approach also isn’t always feasible: In many cases, individual components may not be available with peak current control option. In those cases where components are available, the fixed form factor of many portable electronics and wearables restricts the use of high-leakage, high-powered components in the system design.

Today’s ultra-low-power memories, such as the Cypress Excelon LP F-RAM, are designed to help OEMs control peak/inrush current without the need for external components or special system-level provisioning to enable faster system bootup. In addition, controlled peak current keeps the system’s current within specified limits, which prevents batteries from being overdriven during power-mode transitions.

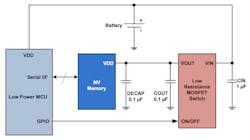

Figure 2 shows a commonly used circuit to control the inrush current as well as low-power-mode current in a system, especially when the peripheral devices aren’t designed with those special features. This circuit maintains high-leakage peripherals in power-off mode and releases them in a sequential manner to keep total system peak current low during bootup.

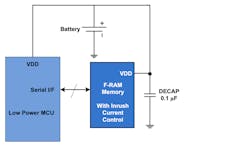

In Figure 3, a standard nonvolatile memory configuration uses a memory design for ultra-low-power applications. The memory has built-in standby and inrush current controls that can help to eliminate the need for external control circuitry, including, as shown here, components like switches, decoupling capacitors, and controller GPIO.

Enhancing Battery Life

As described previously, portable systems often enhance battery life by operating with an extremely low duty cycle to optimize the total power consumption. These systems are put into extremely low-power mode, such as deep-sleep or hibernate, to minimize overall current leakage when not in use.

Modern low-power MCUs are equipped with various low power modes that provide extremely low current leakage, in the range of a few hundreds of nanoamperes (typically 50 to 500 nA). However, peripheral components such as data-logging NV memories (EEPROM, MRAM, or flash) or volatile RAMs often have much higher low-power-mode leakage current, in the range of tens of microamperes. Such high current leakage in peripheral components can easily negate all of the advantages of using low power MCUs, at least until they’re fully turned off using external circuits as shown in Figure 2.

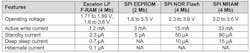

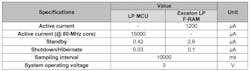

Memory manufacturers are addressing the need for more efficient leakage current in wearables and portable applications. Excelon LP F-RAMs, for example, have an energy-efficient design that helps reduce high current leakage by restricting its standby current to a single-digit microampere and hibernate current in the range of 100 nA. Table 1 compares current consumption in various nonvolatile memories while operating in different power modes. As can be seen, advances in memory technology enable a hibernate leakage current that’s an order of magnitude lower than the standby current and is comparable with MCUs’ hibernate/sleep mode currents.

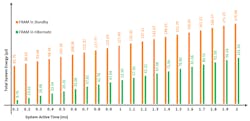

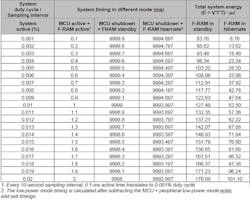

The impact on system battery life impact due to ultra-low-power modes in peripheral devices is shown in Figure 4. Table 2 compares the key current characteristics of a low-power MCU and ultra-low-power nonvolatile memory. These data are used to calculate the total system energy while the system is in active mode and in low-power mode, with varying duty cycles.

Finally, Table 3 provides the system energy calculation and Figure 4 plots the result.

The use case discussed in Figure 4 demonstrates that if a system wakes up every 10 seconds and remain active for 100 µs, the total energy consumption can be reduced by an order of magnitude when putting the nonvolatile memory in hibernate mode rather than in standby. This configuration can enhance system per charge battery life by a factor of ~10X. However, as the activity factor increases, this reduces system standby-mode time, thus reducing the impact on battery life savings. As a result, having multiple low power modes allows system to optimize energy efficiency and performance without requiring extra circuits or components.

Ultra-low-power memories offer multiple low-power modes. The Cypress Excelon LP F-RAM, for example, has three different low-power modes: standby, deep-power-down, and hibernate. These optimized operating modes allow OEMs to significantly reduce power consumption, extend battery life, and control peak/inrush current to enable next-generation portable medical, wearable, and IoT devices.

Shivendra Singh is an Applications Er. Sr. Principal at Cypress Semiconductor.