Nondestructive memory BIST for runtime automotive test

Achieving functional safety levels mandated by the ISO 26262 standard requires periodic testing of a vehicle’s electronics. This testing can be applied at three distinct time periods, each with its own constraints: key on, key off, and during operation.

Key-on testing must provide coverage of all critical components within a very limited time budget. Testing cannot add too much time to the overall powering-up process, as drivers and passengers will not tolerate having to wait for the vehicle to begin operating. In contrast, Key-off testing removes these time constraints as the vehicle’s electronics can continue to remain powered after the driver presses the off button for as long as necessary to complete any level of testing.

The most challenging period for testing is, no doubt, when the vehicle is operating. Testing of the electronics must be performed with the added burden of not affecting the vehicle’s normal operation. There are generally two approaches to achieving this form of testing. In software-assisted test, the specific electronic components to be tested are taken offline by software to allow testing to be carried out. In the case of memory testing, for example, a memory BIST controller is given exclusive access to the memory under test and can access all locations within it. This usage model requires that the system software be involved in and aware of the testing process. It must disable and then re-enable the target memory before and after testing as well as save and restore the memory contents as the memory BIST test will erase any previous data stored in the memory. In addition to requiring complex software support, the software-assisted testing approach will generally result in system performance impacts due to the periodic unavailability of the memories under test.

A more desirable testing approach is one that is software-transparent—that is, an approach that allows testing to occur without the system software having to perform any housekeeping and that does not result in any significant system performance impacts. Nondestructive memory BIST is one such solution for memory testing. With this solution, the memory under test is not taken offline, its contents do not need to be restored after testing, and there is little to no impact on system performance.

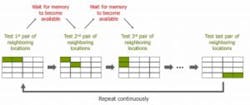

In the nondestructive memory BIST approach, a memory is tested by a series of short sequences of transactions, known as bursts. Each burst is a separate memory BIST session. Typically, a burst requires less than 20 clock cycles to complete and targets a different pair of memory locations each time, allowing all locations in a memory to be tested over multiple memory BIST sessions, as illustrated in Figure 1.

Memory locations that are modified by a burst are saved and restored during each burst by the memory BIST controller. A burst consists of the following steps:

The memory BIST controller releases the request.

overall system performance is very small as the percentage of time any given memory is being tested will range between only 0.1% and 1%. In addition, most processors make use of data and instruction buffering, which further reduces the probability of a pipeline stall.The effects of the nondestructive memory test on performance are further reduced by minimizing the complexity of the test algorithm used. Since all of the memories have already passed comprehensive production testing, it is safe to assume that any defects encountered in the field are mainly due to transistor aging and electromigration effects. The full production test can also always be applied during power-on testing if there are any concerns about coverage of other defect types. An algorithm for the runtime nondestructive test can then be used that only targets defects of the following nature:

- bit-cell stuck-at faults due to aging transistors,

- bit-cell transition faults due to aging transistors,

- coupling faults between two memory locations,

- word-line timing faults due to electromigration,

- via/contact wear-out due to electromigration, and

- sense amp failure due to aging transistors.

The algorithm should also be applied at-speed as many of the above defect types will result in performance degradation. A key aspect of any nondestructive algorithm is that it must first read and store the contents of the memory locations to be tested in the given burst and then write the values back at the end of the burst. This inherent manipulation of functional memory values lends itself to other useful features as well. Probably the most interesting of these is the ability to perform data scrubbing to prevent soft ECC errors from accumulating. When the memory BIST controller reads the two memory contents at the beginning of the burst, it also reads the corresponding ECC code values, checks if there is an ECC error, and if so writes back the corrected values at the end of the burst. This provides a further increase in the device’s ongoing reliable operation as it helps to ensure that the ECC logic can continue to correct soft errors over time.

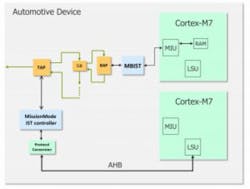

Figure 3 illustrates a sample device architecture implementing a nondestructive memory BIST solution based on Mentor’s Tessent MissionMode in-system test (IST) controller and ARM Cortex-M7 processors.

The IST controller supports communication between various DFT resources throughout the chip and a CPU inside or outside the device. An IEEE 1687 (IJTAG)-based network is used

to provide access to all of the BIST controllers distributed throughout the design. In this example, the CPU used is the Cortex-M7 processor as it natively supports the necessary memory BIST handshaking. It is, of course, possible to implement the necessary handshaking logic within any processor or SOC architecture.

In this architecture, each memory BIST burst is initiated by the bottom M7 processor. The processor’s load store unit (LSU) sends the necessary command to the IST controller through the popular ARM AMBA high-performance bus (AHB). The IST controller, in turn, sends the necessary command through the IJTAG network to the memory BIST controller to apply the next burst of its nondestructive test. Upon receiving this command, the memory BIST controller initiates a request to the top M7’s memory interface unit (MIU) to access the memory it is currently testing. When ready, the MIU performs the necessary operations to take the requested memory offline for testing. The memory BIST controller in this sample architecture can be used for production test as well, reducing the overhead of adopting both test solutions.

Conclusion

The need for runtime testing of automotive electronic components will no doubt continue to grow as an increasing amount of ADAS and autonomous-drive functionality is incorporated into automotive systems. Nondestructive memory BIST offers a software-transparent approach to achieving this functionality for the memory portion of devices. Although some ad hoc techniques already exist for runtime testing of other portions of the device, more effective solutions will be needed to meet the needs of growing automotive design complexities.

About the author

Stephen Pateras is product marketing director within the Silicon Test Solutions group of Mentor, a Siemens Business. He has responsibility for the company’s BIST and automotive products. He received his Ph.D. in Electrical Engineering from McGill University in Montreal, Canada. [email protected].