2021 Special Report: Mil/Aero Test

Download this article as in PDF format.

The need to create, develop, field, and support reconfigurable multipurpose radar, EW, and military comms creates system-level architectural and I/O concerns. Serving a networked infrastructure with high data-throughput and low latency is critical.

Today’s military and aerospace systems rely on a high-speed I/O to support the high data rates used with these devices, as well as that among sensor, memory, storage, and graphics subsystems. Advanced military/aerospace-specified data acquisition and I/O platforms must often be housed in a rugged chassis, and must support virtually any input, any sensor, or any interface I/O.

Secure for Mil/Aero Apps

When we reached out to Rohde & Schwarz, we received responses back from Albert Ramirez, AeroDef market segment manager, and Darren McCarthy, technical marketing manager. Ramirez told us the main interface control solutions used by their government customers are the Gbit/s LAN (providing 125 MHz BW) or the USB 3.0 (providing 120 MHz BW) ) interface and due to mil-secure restrictions, the recommended protocol is Secure VISA or HiSlip 2.0 from the XLI consortium.

At the core of HiSLIP 2.0 is the ability to encrypt connections with the Transport Layer Security (TLS) protocol. Each HiSLIP 2.0 compatible device has to be able to identify itself with an X.509 certificate. This certificate needs to be part of a chain of trust. LXI devices supporting the Security Extended Feature get equipped with an X.509 certificate, which is signed by a trustworthy LXI root certificate. The device certificate is checked when establishing the TLS connection.

Application areas such as satellite communications (SATCOM), radar, EWS sensors, as well as 4G and 5G military communications, are all increasing in frequency and bandwidth. Secure VISA-compatible instruments can provide a reliable, secure, and fast interface to control the instrument remotely. The big challenge is the backwards link, where the amount of data that the instrument can transfer back to the controller device (usually a computer) is the bottleneck. Nowadays, it is not possible to transfer complete digital waveforms over 1 Ghz or 120 Mbits BW.

R&S offers a combined solution to control the instruments through Secure VISA and capture waveforms in specific instruments such the R&S IPR Data Recorder, which enables real-time recording of up to 100MSamples/s and issues a statement of volatility—a very important requirement for military customers.

High-Speed I/O

Ramirez explained there is interest in evolving the Gigabit LAN interface into a 100Gbit LAN interface. However, these are plans for the future, as there is not yet enough demand justifying investment of such magnitude on the military or defense market. However, we might see instrument evolutions driven by the commercial wireless market that will be leveraged by the defense industry. One of the biggest demands is connectivity, addressed by such products as the R&S ZNBT, a multiport vector network analyzer offering up to 24 integrated test ports.

McCarthy said that, aside from I/O connectivity for command and control, for early development and R&D, their customers need access to digital IQ data with wide bandwidth, high fidelity, and low latency. Commercial industry standards for mechanical/electrical plugging are several generations ahead of military I/O standards. Interfaces such as the Quad Small Form-Factor pluggable (QSFP+ and QSFP28) can provide data rates from 40 Gbps to 100 Gbps today.

To enable access for digital IQ data, Rohde & Schwarz offers commercial QSFP family plugging interfaces to meet customer needs along with options for streaming unencrypted digital IQ data. To address the need for more bits and bandwidth, R&S continues to offer development platforms with wideband capabilities internally, such as signal generation with bandwidths to 2 GHz and signal analysis to bandwidth of 8.3 GHz.

Digital I/O

However, getting digital IQ signals corrected and data out of these platforms with minimal latency tends to be a challenge, and will lag the development of the internal tools. This is due to the development of the digital I/O interfaces as well as the need for more powerful DSP to perform the real-time signal conditioning. They have customers that use digital IQ data through high-speed I/Os in both signal-ended applications and low-latency loopback applications with hardware-in-the-loop (HIL).

Single-ended applications include capturing signals into deep memory or streaming signals from memory into a signal generator for scenario replay and receiver testing. The low-latency HIL applications range from the development of regenerative satellites and radio links to radar echo generation and electronic countermeasure development such as Digital RF Memories (DRFMs). For high-speed digital IQ data streaming applications, Rohde & Schwarz uses the QSFP (QSFP+ and QSFP28) family of mechanical/electrical plugging standards. One of the main advantages of this compact implementation is the low latency (< 1us).

Emulate and test

Jon Semancik, director of marketing at Marvin Test Solutions, brought up their GX5296 Dynamic Digital I/O with per-channel timing, programmable logic levels, and PMU PXI Card. It enables you to set timing per pin, with multiple time sets and a flexible sequencer, offering 32 input/output channels with PMU per pin and a 125 MHz vector rate (Figure 2). Additional features 64 M Vectors per channel (64 Mb per channel vector memory) and a per-channel drive/sense voltage range of -2 V to +7 V, with four additional control/ timing channels with programmable levels & PMU.

The GX5296 offers advanced dynamic digital I/O performance and capabilities in a single slot, 3U PXI format. The 32-channel, GX5296 features timing per pin, multiple time sets, data formatting, and an advanced sequencer—providing users with the capability to emulate and test complex digital buses for system, board or device test applications. Offering sub-nanosecond edge placement resolution per pin and a PMU per pin, the GX5296 has the ability to perform both DC and AC parametric testing.

Each digital channel can be individually programmed for a drive hi, drive lo, sense hi, sense lo, and load value (with commutation voltage level). In addition, each channel offers a parametric measurement unit (PMU) providing users with the capability to perform parallel DC measurements on the DUT (device under test).

The GX5296 supports deep pattern memory by offering 64 Mb per pin of vector memory with dynamic per-pin direction control and with test rates up to 125 MHz. The board supports both stimulus/response and real-time compare modes of operation, allowing the user to maximize test throughput for go/no-go testing of components and UUTs that require deep memory test patterns. The single board design supports both master and slave functionality without the use of add-on modules.

16-bit Digitizer

GX2482 series high performance, dual differential channel, 16-bit digitizers offer high dynamic range and excellent SFDR (Figure 3). The module’s differential inputs, coupled with its low distortion, makes it a suitable instrument for analyzing high-performance or low-level analog signals. Each channel offers 3 selectable low pass filters, a 16 bit, 180 MS/s ADC, and 64 M words of memory for each channel.

A PLL clock generator is combined with dedicated clock dividers for each digitizer channel, providing independent clocking and flexibility for each channel. The sample rate can be programmed from 1 MHz to 180 MHz. The module is available as a PXI hybrid slot compatible (GX2482) or PXI express compatible (GX2482e) instrument.

The GX3722 is a user configurable, FPGA-based, 3U PXI card which employs a multifunction, analog/digital, I/O daughter board. The module offers multiple analog and digital source/measure capability. The daughter board interfaces to the GX3700 FPGA baseboard, which employs the Altera Stratix III FPGA. The square wave generators can support frequencies up to 8 MHz and feature high bandwidth signal performance. The time-interval analyzers employ high-bandwidth comparators, and can operate to 10 MHz. The function generators provide sinewave and arbitrary-waveform capability. Maximum frequency of operation is 20 KHz. The two-channel, 12 bit, 10 MS/s digitizer includes signal conditioning.

The demand for data

Semancik pointed out that independent pin resources are also essential for many applications. For example, the GX5295’s pin-assigned electronic resources are independent on a per-channel basis and include a full-featured PMU for DC characterization of DUTs. The PMU can operate in a force voltage/measure current mode or force current/measure voltage mode. In addition, the driver and receiver can be configured to support differential input and output signals from and to the UUT.

Sequencer flexibility is also a common request. The GX5295’s sequencer can halt or pause on a defined address or loop through the entire memory as well as loop on a defined address range or through a defined block of memory. Two modes of digital test are also supported: a stimulus/response and a real-time compare mode. The stimulus/response mode is used for driving and capturing data. Alternatively, for digital tests requiring long test vectors, the real-time compare mode can be used to significantly shorten overall test times by comparing in real-time, expected test results and logging only failed vectors and resultant test results (pass or fail).

The company offers an O-Level and I-Level military tester portfolio that includes many testers for launchers, pylons, bomb racks and other armament systems, including the MTS-3060A Universal O-Level Armament Systems Tester. Production acceptance and depot-level testers combine COTS and custom products to provide the most cost-effective solutions to our customers. These testers are based on the open architecture, card modular, PXI standard and incorporate the ATEasy Test Executive software.

Most instrumentation and high-speed I/O solutions, as well as test system solutions offered by MTS are based on the open architecture, card modular, PXI standard and incorporate the ATEasy Test Executive software. MTS also offers a complete line of high-performance FPGA-based solutions with mezzanine cards providing specific functionality, including digital I/O and analog interfaces to the device under test.

Moving data

Keysight’s response, provided by John S Hansen, Aerospace & Defense Strategic Planning, was from an RF/IQ data transport perspective, using high-speed interfaces in TE, rather than testing them. Requirements for transporting massive amounts of data are continuously more rigorous. RF signal data must represent wider and wider bandwidths with more dynamic range. Especially in the realm of electronic warfare, where test and simulation solutions must me multimodal and flexible, like Keysight's EW Threat Simulation & Analysis solutions (Figure 4).

This, coupled with the need to manipulate or analyze the data in real time, can quickly stress the I/O infrastructure of the system. In addition to the performance parameters of the I/O architecture, the solution must be interoperable at all its interfaces. In general, for connections of more than just a few centimeters, an optical solution must be utilized. This creates a pressure to use more optical connections, and the need to use standard interfaces for interoperability.

At the physical level, optical fiber connections are often needed to handle the magnitude of the data. Common protocol standards like 10GbE and 100GbE are preferred for many applications but other less common interfaces may be better suited for their higher throughput, timestamping capability, and the type of transport supported such as VITA-49. The RF bandwidth requirements are increasing; thus, driving the need for higher data throughput for the test system.

Fast Acquisition

Patrick Rule Sr., sales manager with Pacific Instruments, a VPG brand, told us about their Model 5800 Ruggedized Transient Recorder, which can sample any sensor input at up to 10 Ms/s (Figure 5). Nonvolatile memory is stored directly inside the hardened DAQ, to be debriefed later. This removes reliance on any rotating hard drives or operating systems that can fail, resulting in assurance that data will be recorded during destructive and nonrepeatable tests.

Multiple sample rates during very precise timing increments set by the operator allow for higher sampling and lower sampling to take place at predefined time slices with high resolution. For example, sampling can be set to 500ks/s prior to a predefined triggered event from T -.05 seconds to T 0 and set for sampling of 10Ms/s at T 0 to T .5 seconds. This allows for a mix of high- and low-speed sampling in a single data file for more precise time control to capture desired data and not be overwhelmed with massive amounts of undesirable data.

Data Redundancy is often a concern with high-speed tests, as these types of test are typically fatal to the test article and cannot be run more than once. Assurance in data capture is paramount. Pacific Instruments’ systems offer multiple recording points for data recording redundancy. The amount of data from high-speed tests can be overwhelming. Pacific Instruments provides the ability to decimate data by a factor of x both during and after recording.

Rule explained that rocket engine testing generally requires data before and after the test event for certain durations. Pacific Instruments allows the operator to decimate on the fly at desired time increments. For example, 2 ks/s for all channels prior to rocket firing, 200 ks/s during rocket firing, and 200 s/s during rocket engine cool down. Enabling the test technicians to modify the sample rates as desired during the test, instead of having to take data at the full high-speed rate, allows for a much more manageable data file.

Remote operation of the DAQ is often necessary in high-speed tests as personnel cannot be located anywhere near a type of test usually requiring high speed, such as in jet turbine, rocket engine, explosive, and wind tunnel applications. The ability to either have the data acquisition system located far away from the test area for operator control or near/on the test article for remote control is very important to mil/aero customers.

More and faster

Rule mentioned that many test environments are asking for more and more channels at faster and faster sampling speeds, significantly increasing the amount of data. The ability to decimate data on the fly for longer duration high-speed tests, or accurately determine specific times in which to sample, is becoming a highly desired capability in order to significantly cut down on the amount of data.

Being able to use more than just Analog and Digital inputs and to leverage newer technologies such as Digital Image Correlation (DIC), fiber optic strain gage systems, wireless sensors, and load control systems is becoming more and more desirable. Pacific Instruments can input any of these third-party data streams and record, display and broadcast data in parallel to analog and digital data.

Pacific Instruments provides high-end signal conditioning and data acquisition system solutions to rocket engine, jet and gas turbine, wind tunnel, and explosive testing environments for both military and aerospace applications. Pacific Instruments offers the unique ability to input any type and number of sensors, and allows for each input to be set up independently, for example, sample rate, gain, filter, excitation, etc. Systems are available from 1 to 8,192 channels and can sample at up to 10 Ms/s per, along with digital I/O for real-time control with a turnkey software package.

Rule brought up that the company uses true analog signal conditioning ahead of a high-speed digitizer in the same system, allowing for very clean signals in a single turnkey transient data acquisition system. Onboard nonvolatile memory per channel allows for data to be recorded inside the system at up to 10 Ms/s. A ruggedized enclosure housing channel input I/O modules allows for the system to be placed on or near the test article and enables it to withstand violent testing applications. Data is debriefed from the system to any Microsoft Windows-based PC post-test for analysis.

Current trends in high-speed data acquisition in the military and aerospace environments are to have more and more data, either from adding additional channels to a test, or increasing the sampling rate, or both. While more data is not a bad thing, unless you’re the one analyzing all of that data, the key is to not just have more data that is inaccurate, but more data that is precise and tells you accurately what transpired during the test.

Takemi Iguchi is a technical advisory manager at Kikusui America, and he told us about how as the development of the More Electric Aircraft (MEA) increased, Kikusui set out to create a power supply for testing bidirectional converters connected between the AC bus and HVDC bus. For example, the PCR-WE2 series is adaptable with both buses and can be used as a power source for development and evaluation tests (Figure 6). Three outputs can be set independently so that different voltage combinations (including AC and DC combinations) are possible.

Iguchi reminded us that conventional AC power supplies are unable to sink power, requiring a resistive load and an electronic load device to be connected in parallel. In addition, since these load devices convert the absorbed energy into heat, there are challenges treating the heat exhaust. With a regenerative AC power supply solution, the source and sink can be covered by a single power source. In addition to reducing equipment installation space, energy is not processed as heat, but regenerated to the grid, creating an environmentally friendly test system.

Creative design

Brandon Treece, principal solutions marketing manager at NI, was quick to point out that the company takes an interesting approach to high-speed I/O for digital interfacing applications. By combining customizable FPGA-enabled COTS hardware, with powerful software and IP libraries both from NI and their network of partner companies, they are able to help customers create a high-performance solution, while reducing risk typically seen with the traditional approach.

NI has many different models available, in three categories, each with a user-programmable FPGA that varies in speed and customizability. For example, in high-density single-ended digital applications, NI offers a reconfigurable I/O line of PXI modules with up to 128 FPGA controlled digital lines in a single PXI slot, each capable of speeds up to 80 MHz (Figure 7). For high-speed serial communication, they have high-speed serial instruments offering speeds up to 28 Gbits/s.

Traditionally, to address these applications, engineers would need to develop this type of capability from scratch using traditional FPGA development tools. With this platform, you can design reconfigurable, high-performance testers that meet custom requirements from a higher-level starting point, directly out of the box, reducing engineering needs in the creation of the solution.

Treece also said there are several challenges when it comes to digital-interfacing applications in mil/aero applications that often center around flexibility and performance. On the one hand, if an application requires simple communication over a common interface bus such as MIL-STD-1553 or ARINC-429, there are a plethora of options available on the market to address this need.

However, if the application requires a customized version of a protocol; a complex high-speed protocol such as Fibre Channel, Serial Rapid IO (SRIO), or ARINC-818; or in some cases a customized version of a complex protocol COTS, hardware and software often isn’t available so custom design is required. NI addresses these challenges by providing customizable FPGA-enabled COTS hardware, with powerful software and IP libraries, both from NI and its network of partner companies that provides a higher-level starting point for engineers to use, and avoid all of the risk that comes with custom design across the design cycle.

Connection migration

Treece explained they are seeing a move from parallel digital buses to complex, high-speed serial protocols like ARINC-818 and Serial Rapid IO (SRIO). This is causing challenges for engineers and test teams as they are faced with implementing these protocols while still holding to their schedule. Even with off-the-shelf IP cores, implementing a custom design introduces significant risk, and being able to leverage customizable FPGA-enabled COTS hardware reduces the risks associated with custom design.

He was proud to point out that NI’s very first customer back in 1977 was Kelly Air Force Base in Texas, and today provides platforms that include modular hardware like VXI, PXI, and CompactRIO, and engineering software like LabVIEW, LabWindows/CVI, TestStand, and more. Along with these commercial tools, NI has developed a deep knowledge of the challenges test teams face in technical development, requirements changes, and business impact—not only in the aerospace and defense industries, but others as well.

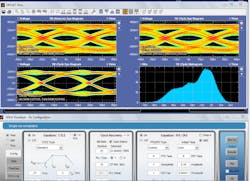

Tektronix’s Brad Odhner emphasized how Tektronix offers solutions for the latest high-speed I/O standards, including mil/aero test system favorites like Serial Rapid I/O (SRIO), Fiber channel, ARINC 818, XAUI, as well as custom busses at speeds up to 32 Gb/s. The Technical Marketing Manager pointed out that this is enabled by their high-speed oscilloscopes such as the recently released 10 GHz 6 Series B MSO and the 70 GHz DPO70000SX platform, and their toolsets.

DPOJET software for the DPO70000SX platform provides industry-leading jitter analysis and eye-diagram evaluation, allowing in-depth debug and complete characterization on serial buses to verify signal integrity. The Advanced Jitter Analysis software for the Tektronix 6 Series B MSO is based on, and is very similar to, DPOJET. Serial Data Link Analysis (SDLA) software and the DPO70000SX platform can emulate complex scenarios on real, measured waveforms, in addition to theoretical simulation that relies on idealized signals.

Odhner explained that SDLA provides the ability to de-embed necessary fixtures and cable sets to deliver the signals to the oscilloscope, and allows for embedding channels or cable sets that engineers might not physically have at the time of test, to see how signals will change through different signal paths. SDLA also enables engineers to work through “what-if” scenarios for Tx and Rx equalization settings, to determine how they affect signal integrity (Figure 8).

Odhner sees mil/aero engineers adopting more and more high-speed serial buses that have already existed in the commercial space. The challenge for these engineers is that they don’t follow the same use models that these buses were intended for; often driving signals over special interconnects and longer than allowed spans. Our toolsets are flexible enough to enable engineers to continue development in these odd environments.

Another common challenge is the need to measure a bit-error ratio (BER) on these special links. Traditionally this requires a single-use piece of equipment, a BER tester or BERT. Their DPO70000SX oscilloscopes have an optional error-detector built into their hardware, enabling them to, alongside their oscilloscope functionality, perform these BER measurements without the need of an additional instrument (Figure 9). Additionally, unlike a BERT, BER testing with the DPO70000SX can be done directly through the oscilloscope’s probing interface.

In radar, sensors and electronic warfare, we are seeing more standardization in backplane connectors, owing to the new modular open systems architectures (MOSA) program in the U.S. These standardized connectors are translating into a more specific set of protocol testing needs, which include multi-gigabit ethernet (10 Gbe) and PCIe Gen3 (8Gbps). They’ve seen higher demand for the ability to characterize, debug and verify high-speed serial subsystems. In terms of protocols, we’ve also seen a fair amount of DDR.

Tektronix pioneered the use of silicon-germanium-based hardware in order to achieve the performance that customers need. The Asynchronous Time Interleaving, or ATI, technology in their DPO70000SX platform allows the oscilloscope to retain a high signal-to-noise ratio at higher bandwidths. They also develop custom ASICs for their oscilloscopes for high speed I/O. For example, with the Tektronix 6 Series B MSO, a custom ASIC allows engineers to view frequency and time-domain signals simultaneously, with industry-leading low noise and 12 bits of vertical resolution.

Odhner said the company expects the need for increased data and bandwidth throughput through adoption of higher data-rate protocols such as PCIe Gen 4 (16Gbps). Customers expect solutions to be backward-compatible with previous generations, and will demand as much software automation as is possible. They also anticipate more requests for optical solutions.

Captured at speed

When we reached out to Rodger Hosking, a VP at Pentek, he highlighted the company’s recently introduced Model 2757 100Gb Ethernet Recorder, which captures full-speed streaming data to SSD drives at sustained rates of 12.5 GBytes/s. It supports UDP Ethernet protocol over optical cable, which is popular for real-time data links because of its low overhead.

Hosking said that interfaces are becoming faster because of increased signal bandwidths, along with the number of channels, as well as requiring higher resolution and dynamic range in virtually all sensor systems.

One technique to solve this is to perform DSP operations closer to the antenna, by extracting or qualifying only relevant information at the source, before sending raw data through system interconnects. Many I/O links are shifting from copper to optical cables for many benefits: higher speed, immunity to EMI, and longer cable spans. Smaller and lighter-weight cables are especially important for UAVs, and secure radiation-free optical cables make eavesdropping difficult.

Hosking said that Pentek supplies many test solutions for radar, EW, countermeasures, and communications systems, including digitizers and recording systems to both capture and generate these signals. Design cycles need to get shorter in spite of complexity, so developers of test systems can benefit by incorporating higher-level elements in their designs—like sub-systems instead of discrete components—to reduce risk and save time.