What’s the Difference Between SPICE and FastSPICE Circuit Simulators?

This file type includes high-resolution graphics and schematics when applicable.

Circuit simulators are among the most important electronic-design-automation (EDA) design tools for IC design. Circuit designers rely on them to validate their design ideas, simulate the electrical behavior and performance of their designs, and verify designs before tapeout. Simulation accuracy, performance, and capacity are the significant criteria for selecting a circuit simulator.

Often, technology advances also lead to reduced supply voltage, increased parasitic effect of wires relative to the transistor, and more severe impact from process variations, such as global and local random variations, layout proximity effects, and bias-temperature-independent (BTI) reliability effects. As a result, the actual design margins are shrinking.

No doubt, these trends make designs more difficult and require higher accuracy of circuit simulations. Low-power design for mobile, Internet of Things (IoT), and wearable applications adds further requirements on simulation accuracy, such as accurate verification of timing, power, and leakage, in the final verification and sign-off stage.

Meanwhile, chip size is on the rise, chasing Moore’s Law. Multi-million or even multi-billion transistor counts are commonplace in leading-edge chip designs. The technology moving to 3D FinFET further increases circuit sizes due to extra parasitic components in FinFET compared to its bulk-silicon counterparts.

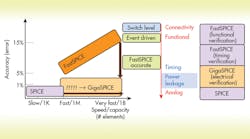

This trend adds to simulation capacity and needs circuit simulations to run faster. Requirements on accuracy, capacity, and performance have been driving the evolution of the circuit simulator over the past 20 years, leading to two main types of transistor-level simulators: SPICE for high accuracy, and FastSPICE for large capacity and high performance.

SPICE

SPICE is the golden circuit simulator used to verify designs. Due to capacity and performance limitations of SPICE simulators, design teams have come to rely on FastSPICE for large block or full-chip circuit verification and signoff. Examples include large embedded memory of system-on-chip (SoC) or memory-chip designs.

SPICE was first developed at the University of California at Berkeley in the 1970s and later commercialized into different tools such as HSPICE, which is still in use today.

Once the limitations of traditional SPICE simulators became apparent, Parallel SPICE was developed to overcome circuit size and performance limitations. Some popular commercial tools in this group include Spectre APS, FineSim, AFS, and NanoSpice.

One big advantage with SPICE is accuracy –– all SPICE or Parallel SPICE simulators should solve single matrix and calculate full equations to maintain the highest accuracy. Commercially available Parallel SPICE simulators handle million-element circuits, which works for most analog designs. They can’t handle very large designs that require both high capacity and high accuracy, such as leakage and power verification of advanced memory designs at 20 nm and beyond.

Conversely, FastSPICE employs some special techniques, such as table model, parasitic resistance and capacitance (RC) reduction, matrix partitioning, and hierarchical simulation, trading accuracy to support large simulation capacity and improve performance. Popular FastSPICE tools, such as include FineSim-Pro, CustomSim, and Spectre XPS are often used for large block or full-chip simulation and functional verification.

These event-driven FastSPICE techniques significantly accelerate simulation and allow designers to simulate big circuits. As a result, accuracy is sacrificed and the relative error to golden SPICE may be in the range of 10~15% or more. That’s not acceptable for high-accuracy simulation and verification for high-end memory and SoC design needs at 20 nm and beyond.

FastSPICE Challenges

Timing and power are two characteristics of SoC and memory-IC designs. With embedded memory occupying more than 50% of an SoC’s die area, it becomes the most critical component for timing/performance and power.

On-chip critical timing paths will either start or end at the memory address, data, or control pins. Consequently, accurate timing verification of embedded memory and the full chip becomes critical to achieve high-performance designs. Accurate power verification is crucial for low-power designs, too. In addition to clock circuitry and I/O ring power consumption, embedded-memory power consumption is the most significant factor for on-chip power expenditure.

With reduced supply voltage and the increased impact of process variations, accuracy becomes even more important at advanced nodes. Designers have to capture small current components, such as small leakage current of each transistor, to accurately predict chip leakage current before tapeout.

Another challenge faced by designers when moving to more advanced technologies is the ever-increasing size of memory instances in embedded memory and memory IC designs, such as DRAM and NAND flash memory. Furthermore, 3D FinFET adds more parasitics to the post-layout circuit netlist –– more than 100-million elements becomes quite common for advanced memory characterization and verification. Traditionally, such simulation capacity can only be offered by FastSPICE simulators.

Unfortunately, FastSPICE sacrifices accuracy for performance and capacity. There are increasing concerns about FastSPICE’s accuracy for memory verification and signoff using small technology nodes, which have much narrower design margins than previous nodes.

For example, FastSPICE uses aggressive parasitic and even node reduction to speed up simulation of a large netlist. As a result, designers can’t capture all of the details inside the circuit with FastSPICE simulation. Even worse, the probed result may be wrong, as a 10% accuracy loss would lead to quite significant error for certain small or sensitive measurements like small leakage current or small noise margins.

To avoid aggressive overdesign and increase confidence before tapeout, designers need simulation accuracy for large block or full-chip verifications to be within 5%, or even down to SPICE accuracy level at times. It needs to be fast as well. Apparently, traditional FastSPICE simulators can’t offer such accuracy and performance at the same time. SPICE simulators don’t have the ability to handle big circuit sizes and aren’t fast enough, leading to compromised accuracy and insufficient confidence before tapeout in many advanced design projects saddled with high cost and high risk.

Other FastSPICE Constraints

FastSPICE also exhibits other limitations for those applications. Users often need to try complicated and different option settings to trade off accuracy and performance for different circuit types. It takes some effort to find the correct circuit-specific option for each circuit type. Such fine-tuning lowers the user’s confidence about the simulation results, though, since it doesn’t always guarantee correct results. When simulation gets it wrong, designers can’t refer to a “golden.”

Unlike pure SPICE simulators that can get direct-current (dc) convergence, FastSPICE often runs into non-convergence problems in the initial dc simulation stage, especially for large block designs with parasitic RC under a small supply voltage. Although FastSPICE can continue simulation without a converged dc, there’s a greater chance of unreliable results, decreasing reliability and the robustness of FastSPICE simulation results.

At advanced nodes, FastSPICE is running out of steam as techniques used to accelerate performance either break or face significant difficulties.

With growing accuracy concerns for large-scale simulations that can’t be handled by either SPICE or FastSPICE, new giga-scale SPICE simulators, or GigaSpice, are starting to arrive on the market. Such a new simulator provides a golden reference for FastSPICE and directly replaces it for large block simulation and full-chip verification in the design flow.

GigaSpice offers a pure SPICE engine for guaranteed accuracy and FastSPICE-like capacity, with the ability to handle more than one-billion elements thanks to its innovative data structure and memory-handling techniques. Leveraging advanced parallelization technologies and easy-to-access hardware resources, GigaSpice can also run faster than FastSPICE.

Sometime soon, this article will need a rewrite in order to compare the three different categories of transistor-level circuit simulators.