High-speed serial interfaces for data converters are starting to take shape to support the growing needs of higher-speed converters, flexible clocking requirements, and latency determinism. The first and second versions of the JESD204 serial link provided a much needed breakthrough for converters to send and receive data using a lower pin count. However, these versions had fundamental limits in scope for lane count, speed, and functionality.

A third version, JESD204B, has arrived with three new major enhancements: a higher maximum lane rate (up to 12.5 Gbits/s per channel), support for deterministic latency, and support for harmonic frame clocking. The new JESD204B interface can move large quantities of data easily for processing by taking advantage of higher-performance converters that are compatible and scalable with open-market FPGA solutions.

FPGA companies have been talking about multi-gigabit serializer/deserializer (SERDES) interfaces for several years now. FPGA engineers have long recognized that you need big, fast pipes to get data into and out of FPGAs as fast as the devices can process it. The big problem has been that, in the past, most analog-to-digital converters (ADCs) weren’t wired up with these high-speed serial interfaces. The FPGAs and the ADCs didn’t speak any common language that took advantage of the bandwidth that SERDES can provide.

JESD204B-compliant converters solve this problem, though not without lots of questions. We took a look at some of the top questions engineers had for us on the Analog Devices EngineerZone online support community and would like to share what we’ve collectively learned.

When connecting multiple high-speed digital-to-analog converters (DACs) with parallel I/O to a single FPGA, there will be a huge I/O requirement at the FPGA. In this case, it is difficult to layout and connect data clock out (DCO) signals from each DAC to the FPGA. How can a SERDES interface help with this problem?

The serial JESD204B interface uses significantly fewer I/O pins than a parallel or low-voltage differential signaling (LVDS) interface structure. In addition, the clock is embedded in the serial data stream, so a DCO isn’t necessarily required. Since the JESD204B data is framed at the transmit device and de-framed at the receive device using control symbols for alignment, the inter-pair skew between I/O lanes is largely forgiving to the point of not being a large concern in layout. This makes the I/O layout complexity from your FPGA to your ADC or DAC much easier, and your printed-circuit board (PCB) layout engineer will thank you.

Related Articles

• Faster JESD204B Standard Presents Verification Challenges

• JESD204B Converters Simplify FPGA And ASIC Interfacing

• New JESD204B Interface Speeds And Simplifies ADC To FPGA Interconnection

As an example, the JESD204B specification calls for the receiver to be able to de-skew data from multiple transmitters across lanes that can be skewed as far apart in time as 68 unit intervals (UI). This means that the total skew for a 6.25-Gbit/s lane rate can be 68 x 160 ps = 10.88 ns, while allowable skew for a 12.5-Gbit/s lane rate can still be 68 x 80 ps = 5.44 ns. Granted, for this entire skew budget, some portion must be allocated for serialization first in, first out (FIFO) skew in the JESD204B transmitter. However, if put purely into terms of lane length mismatch for 6.25-Gbit/s and 12.5-Gbit/s lane rates, this would equate to 61.8 and 30.9 inches of skew respectively (assuming an FR-4 material relative permittivity of about 4.3). This should provide enough skew margin to comfortably route lanes in a system without concern.

The alignment process in my application is traditionally completed with a digital ASIC (FPGA) and most often includes ADCs. With the update from the JESD204A to JESD204B serial standard, a new signal called SYSREF is used to achieve deterministic latency between multiple converters. Is there a need for a central clock unit to provide the clocks and SYSREF signal that will be required when moving to the JESD204B interface? How do you ensure alignment with the analog circuits that are provided?

The system reference signal, or SYSREF, is a subclass 1 feature of the JESD204B interface. It is used to create known deterministic latency from the ADC to the FPGA. When an application needs multiple converters to be aligned synchronously, care needs to be taken in layout so the SYSREF signal arrives with known accuracy, relative to a particular clock edge, across the multiple converters. Harmonic clocking support now allows a transmitter and receiver device to share the same device clock or its harmonic as opposed to sharing an internally generated framing clock.While several clocking structures may be able to achieve this feat, a central source clock generator may provide the best option because the SYSREF signal must be source synchronous to the clock(s). The AD9525 3.6-GHz clock generator also provides a SYSREF signal output source synchronous to the output clocks.

Can the converter’s SERDES interface be modeled?

The JESD204B physical layer (PHY) of an ADC or DAC can be modeled using what is known as an IBIS-AMI model (I/O Buffer Information Specification-Algorithmic Modeling Interface). IBIS-AMI not only provides the I/O characteristics of the pin, it also offers a way to simulate the behavioral algorithm of the PHY layer. With this capability, system designers can measure the impact of jitter, rise/fall times, pre-emphasis, and equalization within the signal path of their systems.

This type of model provides several advantages for system designers. It’s interoperable with many advanced simulation packages, so models from different semiconductor vendors can be run together to simulate both ends of a link. Users can set the silicon control parameters in the IBIS-AMI model as needed for their system and even simulate a matrix of options to find the best case profile. And with the model’s efficient performance, multimillion-point simulations can be run in a matter of minutes.

I found a parameter called CS (the number of control bits per conversion sample) in the JESD204B specification. It shows that the setting of CS can be 0, 1, 2, or 3. But there is not a detailed description about the function of these control bits in the specification. Which block will generate these bits if I apply it in the JESD204B interface, and what are the functions of these bits?

The JESD204B specification allows for up to three control bits per conversion sample to be appended into the serial data stream. There is clear detail in the specification about the placement of these control bits in the data stream for various JESD204B link configurations. However, the functional assignment of the control bits in the device is left up to the converter design team. Hence, there isn’t a single answer for the functions of these bits, and it can be different among vendors or even within a converter portfolio. The control bit information could be generated in the converter block, the JESD204B interface block, or some intermediate digital processing block, depending on what information is needed. This gives system designers flexibility to assign and use the control bit features that best enhance the performance of their application.

System designers can expect to use several JESD204B control bit functions: analog over-range or under-range of an absolute or variable level, trigger start/stop function, data valid, or to indicate a specific converter processing function such as a digital filter. A typical use for the control bits would be to have an FPGA interpret the real-time information and make decisions for the system, such as adaptive amplifier gain or alignment of data.

What flexibility do I have in my design for changes to the JESD204B lane rate and lane count? Am I forced to use all the lanes, even if I don’t need all the bandwidth for my application?

A typical configuration of the JESD204B interface uses one or more lanes that scale in frequency at some multiple relative to the converter clock rate. In addition, several wideband converters have multiple phase-locked loop (PLL) ranges that let designers use a lower lane count when their system uses a slower converter clock. Some converters provide internal digital processing blocks, such as decimation filters in ADCs and interpolation in DACs, that reduce the need for the full data rate to be transmitted over a JESD204B link.

An alternative to these approaches is to pack the converter data more efficiently on the JESD204B link, where no additional information can be sent other than the raw converter samples. An application then can use an otherwise slower lane rate or a lower lane count at the expense of a loss of control bit information. Control bits require the space afforded from a less efficient packing scheme. For these cases, it is important for system designers to understand the tradeoffs for their application. The exact lane rate, lane count, and data packing for each converter depends on the converter clock rate, the resolution, and the particular design implementation in the silicon.

How can I validate that the JESD204B link is working correctly in my system application, independent of the converter operation?

JESD204B calls for some mandatory test patterns to be made available on the link by the transmitter. These patterns are necessary to be able to validate the data integrity of the serial interface. One set of patterns sends a continuous sequence of pre-determined control characters that will allow the testing of jitter, code group synchronization, and a receiver eye mask. Another pattern sends a repeated initial lane alignment sequence request to the receiver. A final set contains pseudorandom and pre-determined data with varying lengths of repetition. These patterns can be used to test the bit error rate (BER) on the link, as both the transmitter and receiver know the expected sequence of data.

I’m implementing a JESD204B de-framer in FPGA code and need to know whether the scrambler is required. If so, what is the benefit of using it?

The scrambler feature for JESD204B isn’t required, but it may help some applications remove digital framing repetition that could cause unwanted harmonic noise in sensitive systems. It provides a method to eliminate spectral peaking on the link due to data being sent repetitively at the same point frame to frame. This peaking can be removed by using a known polynomial to mathematically scramble the data at the transmitter and then de-scramble the data at the receiver. The polynomial equation for the JESD204B scrambler allows a sequence period of 32,767 bits, which is long enough to meet most system spectral requirements. For scrambling to be enabled, the JESD204B transmitter and receiver both must first agree to enable the feature, generally by communicating an enable bit in the link configuration parameters.

Does the SYNC+/- signal need to be synchronized to the converter clock?

While the SYNC function should be synchronized to the converter clock or harmonic clock for subclass 0 or subclass 2 operations, it does not have to be when used for JESD204B subclass 1. For the subclass 1 case, only the SYSREF signal needs to be source synchronous to the clock. The SYNC signal originates from the JESD204B receiver or FPGA controller as a means to initiate sample data transfer by aligning the link to control characters. Since this event can happen whenever the receiver requests data, it may or may not be at a synchronous event to the converter clock.

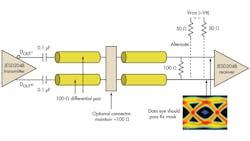

How do I properly terminate my JESD204B output drivers? What should I consider for proper layout?

The differential impedance of each trace pair should be 100 Ω, with a termination of 100 Ω at the receiver. It’s also important not to neglect impedance discontinuities at interconnects and maintain a near 100-Ω differential transmission line over connectors. In general, system layout should aim to minimize signal loss on the JESD204B link and adhere to the interconnect insertion loss mask in the specification for the particular application baud rate. An ac-coupled approach is suggested to mitigate mismatches in common-mode voltages at the transmit and receive devices (see the figure).

Each JESD204B differential lane should be matched in length intra-pair between the +/- signals. While lane to lane, or inter-pair, length matching is not critical, matched lengths within a pair are still important. Any intra-pair trace mismatch will close down the available data eye seen at the receiver, effectively limiting the bandwidth of the link.

Summary

This is just a sampling of the many JESD204B questions and conversations on ADI’s EngineerZone that system designers pose about the new technology. The dialogue is helpful to all levels of engineers as they become involved with next-generation data converters that use JESD204B. As the interface proliferates within the data converter market, complementary performance and IP capabilities on FPGA platforms should help the adoption. Future questions and discussions should only grow, albeit with additional complexity, as more engineers become involved and start designing new systems. As ADI is committed to supporting engineers as they learn about the standard, feel free to send your JESD204B questions to IanB on ADI’s EngineerZone.

Ian Beavers is a staff engineer for the Digital Video Products Group at Analog Devices, Greensboro, N.C. He has worked for the company since 1999 and is a team leader for HDMI and other video interface products. He has over 15 years’ experience in the semiconductor industry. He has earned a bachelor’s degree in electrical engineering from North Carolina State University and an MBA from the University of North Carolina at Greensboro. He can be reached at [email protected].

About the Author

Ian Beavers

Product Engineering Manager, Automation Energy and Sensors, Analog Devices

Ian Beavers is a product engineering manager for the Automation Energy and Sensors Team located at Analog Devices, Greensboro, N.C. He has worked for the company since 1999. Ian has over 20 years of experience in the semiconductor industry. He earned a bachelor’s degree in electrical engineering from North Carolina State University and an M.B.A. from the University of North Carolina at Greensboro.

Voice Your Opinion!

To join the conversation, and become an exclusive member of Electronic Design, create an account today!

Leaders relevant to this article: