Hierarchical Processors Target Wearable Tech

Developers delivering a single product have it easy. Pick a system-on-chip (SoC) microcontroller that meets the application requirements, and refine the software until it works as desired. The design task becomes more complex if more than one product is in the mix, especially if the requirements become more demanding. The typical approach is to have a single-core solution across the board with more powerful processors covering the high end.

These days, a 32-bit processor family can provide code compatibility from the low end to the high end. The low end tends to have lower power requirements but with lower performance. The high end has more performance, but power requirements tend to be significantly higher. Nimble programming can exercise run modes to reduce the amount of power used, though it is still a challenge to hit the low end of the spectrum.

An alternative approach is to incorporate multiple processing cores, usually two. One is a small, low-power core. The other is a larger, more powerful core. Minimal power is used when the larger core is shut down and the low-power core is used alone.

This file type includes high resolution graphics and schematics when applicable.

Four-Stage Product Hierarchy

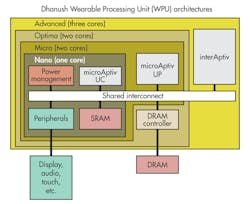

The Ineda Systems Dhanush Wearable Processing Unit (WPU) family spans four upward-compatible platforms based on Imagination Technologies’ MIPS processors (Fig. 1). The smallest, the Nano WPU, is a single-core system based on the MIPS microAptiv UC core (see “MIPS Aptiv Family Brings Consolidation And Raises Performance Bar” at electronicdesign.com). Designed for an always-on operation typical of the target platform, wearable devices, this low-power microcontroller can easily operate as an intelligent sensor hub. It includes the usual peripheral complement and on-chip SRAM.

The Nano is the lone single-core chip in the family. All the other chips are multicore solutions that are built symmetrically. The shared memory and peripherals are equally accessible by each core. The Micro dual-core solution adds a higher-performance microAptiv UP core. Like the Nano, it can run with just the microAptiv UC core using minimal power. The Nano is designed to run for a month on batteries. The other chips in the family should do as well if they are only using the low-end core and on-chip SRAM.

The Optima is essentially the Micro chip with a DRAM controller added. It targets applications that require more memory. By moving off-chip, significantly more storage can be included. The system can run with just the microAptiv UC core using on-chip SRAM to significantly reduce power requirements. This would be handy for delivering sensor hub support without turning on DRAM or the other core.

Finally, there is the Advanced chip (Fig. 2). This triple-core solution simply adds the interAptiv dual core. The programmer must determine which core will run or if all three can provide the best platform for an application. Of course, two of the three may work at some point. This hierarchical approach provides developers with more control over power utilization and performance. The compatibility between cores means programmers do not have to jump through different hoops depending upon which collection of cores is utilized.

As with most microcontroller vendors, Ineda will have a collection of SKUs with different peripheral, memory, and core complements. This includes pulse-width modulation (PWM) timers, analog-to-digital converters (ADCs), and communication ports. Moving up the chain will include more compute performance as well as more memory and peripherals such as hardware accelerators. The display controller on the Advanced will have PowerVR 3D graphics acceleration along with video decode and encode accelerators.

It is possible to take the family to even higher-performance solutions. Ineda Systems has yet to tap Imagination Systems’ high-end proAptiv core. This may take a while as Ineda must deliver and support the current family of chips. The company has a good start, including the SHASTRA software development kit (SDK) and reference platforms. The software includes a unified development environment and power profiling tools.

Wearable technology requires a mix of sensors and low-power operation. The WPU family looks to be an ideal platform to meet those needs, including scaling to devices that have more sophisticated display and input requirements.

About the Author

William Wong Blog

Senior Content Director

Bill's latest articles are listed on this author page, William G. Wong.

The latest blogs have been moved to alt.embedded on Electronic Design.

Bill Wong covers Digital, Embedded, Systems and Software topics at Electronic Design. He writes a number of columns, including Lab Bench and alt.embedded, plus Bill's Workbench hands-on column. Bill is a Georgia Tech alumni with a B.S in Electrical Engineering and a master's degree in computer science for Rutgers, The State University of New Jersey.

He has written a dozen books and was the first Director of PC Labs at PC Magazine. He has worked in the computer and publication industry for almost 40 years and has been with Electronic Design since 2000. He helps run the Mercer Science and Engineering Fair in Mercer County, NJ.

- Check out more articles by Bill Wong on Electronic Design

- Bill Wong on Facebook

- @AltEmbedded on Twitter

Voice Your Opinion!

To join the conversation, and become an exclusive member of Electronic Design, create an account today!

Leaders relevant to this article: