MSP430 MCU Family Expands to 32 Bits

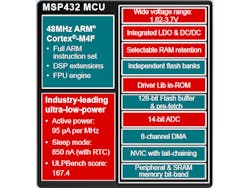

Texas Instruments’ (TI) 16-bit MSP430 microcontroller (MCU) family targets ultra-low power applications, including an all-FRAM-based solution (see “FRAM Microcontroller Targets Low Power Applications”). Now the company has expanded the family with a high-end option, the 32-bit MSP432 based on an ARM Cortex-M4F core (Fig. 1).

TI has higher-performance Cortex-M and Cortex-A solutions with faster clock speeds, which get work done more quickly. However, the MSP432 tops out at 48 MHz—that’s two to four times slower than most Cortex-M4F solutions. This allows for an active performance of 95 µA/MHz. Even with the real-time clock (RTC) running, it can sleep at a mere 850 nA.

EEMBC’s ULPBench is literally the benchmark for low-power microcontrollers (see “Interview: Markus Levy Discusses The EEMBC Ultra Low Power Benchmark”). The MSP432’s ULPBench score is 167.4, and its EEMBC CoreMark score is 3.41/MHz. Quite impressive.

The Cortex-M4F brings digital-signal processing and floating-point to the MSP430 family. The nested vector interrupt controller (NVIC) supports tail chaining, and there’s 8-channel direct memory access (DMA). On the analog side, a 14-bit, 1-Msample/s ADC features a differential mode of operation and 13.2 effective number of bits. It also has a pair of window comparators. The digital side includes four eUSCI_A modules that support UARTs, IrDA, and SPI. Another four eUSCI_B modules support I2C and SPI.

The memory subsystem is equally as impressive—the 128-bit flash buffer and pre-fetch system front-ends dual flash banks allow for reliable in-field updates. The system also provides single-cycle operation. Current incarnations are available with 256 kB of flash, with future versions possibly scaling to 2 MB. There is also a 32-kB ROM that contains MSPWare libraries.

The code security lock lets developers provide code for use, but restricts access to runtime operation only. Four blocks can be protected in this fashion. It also uses encrypted authentication to confirm updates. The code in a block can be called, and that code has access to tables within the block. However, other code cannot access any data within a block.

In addition, the chips contain 64kB of RAM with bit-band support. The RAM is divided into 8-kB blocks that can be selectively disabled, even with respect to low-power operation. Each bank uses 30 nA in RAM retention low-power mode.

TI provides a range of tools, including Code Composer Studio and PinMux, the latter handling the MSP432’s pin remapping feature. They are available with the TI Cloud IDE. The company’s MSPWare includes a driver library as well as support for the ROM runtime. A range of third parties, such as Keil and IAR, support MSP432.

The MSP432 LaunchPad (Fig. 2), priced at $12.99, provides access to BoosterPack boards. It works with ULP Advisor and the EnergyTrace+ real-time power debugging tool that help optimize power utilization. EnergyTrace+ tracks power usage and CPU states, as well as application execution.