Introducing Calibre nmLVS-Recon, which gives designers a systematic methodology for prioritizing and resolving high-impact circuit issues in early design stages. Learn more about the short isolation use model, with three built-in options for analyzing specific areas:

- Targeted short isolation analysis and debugging on incomplete/immature blocks, macros, and chips during early design phases

- Fast iterations of short isolation analysis and debugging, speeding up overall time to tapeout

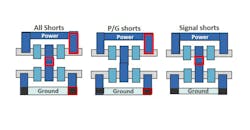

- Partition designs by layer type, layer groups, or net type to support error prioritization