Download this article in .PDF format

With wireless services using ever-higher carrier frequencies and data rates on the rise, the need grows more urgent to provide a way to digitize these signals for processing. That typically means greater demand for faster analog-to-digital converters (ADC). To meet this need, ADCs have emerged with sampling rates of > 1 GHz. This article explains the rationale behind using faster ADCs to implement new and existing applications, and provides an example.

Remembering the Nyquist Rule

When selecting an ADC for high-frequency applications, you should recall that the sampling rate must be two or more times the bandwidth of the signal to be digitized. Such a sampling rate is called the Nyquist frequency. Note that the word bandwidth is used instead of frequency. If the input signal is other than a sine wave, it’s considered to be a complex signal. An example is a pulse that’s made up of a fundamental sine wave and multiple harmonics according to the Fourier theorem. Modulated signals also contain a wide range of frequencies that must be considered when selecting a sampling rate.

Consider a square wave consisting of a fundamental frequency sine wave and an infinite number of odd harmonics. To reproduce a favorable version of the original signal, it has been shown that up to the fifth harmonic must be preserved. For a 300-MHz square wave, the sampling rate must at a minimum be twice the fifth-harmonic frequency, or 3 GHz. More complex signals like radar pulses and modulated signals require similar high sampling rates to faithfully capture the signal details.

An example application is the cellular base-station receiver tasked with processing LTE Advanced signals that use carrier aggregation to give more bandwidth to support higher data rates. Multiple standard 20-MHz LTE channels are grouped to provide 40-, 80-, or 160-MHz bandwidth to support faster OFDM data rates.

Common Applications

The primary application for high-speed ADCs is the software-defined radio (SDR). Most modern SDRs use a direct-conversion (zero IF) architecture in which the input signal is digitized directly after filtering and amplification. With UHF and microwave input frequencies, ADCs must have a high sampling rate. One example is a cellular base-station receiver.

Other common applications include electronic-warfare receivers, RF recording systems, and radar equipment. In addition, fast ADCs are used in test instruments and optical time-domain-reflectometry (OTDR) equipment. Beamforming and multi-user multiple-input multiple-output (MU-MIMO) are other use cases. Fast ADCs are also a critical part of digital pre-distortion (DPD) receivers used in linearizing RF power amplifiers.

Typical of today’s fast ADCs is Texas Instruments’ ADC32RF45. The dual-channel ADC uses a pipeline architecture with a 14-bit resolution. Its maximum sampling rate of 3 Gsamples/s suits it for direct RF conversion receivers for wireless infrastructure in the popular cellular bands from 1700 to 2000 MHz. The input bandwidth is set by the sampling rate divided by two, which produces a maximum bandwidth of 1.5 GHz. The bandwidth may be affected by any filters and amplifiers in the signal chain. Other key specifications are spurious free dynamic range (SFDR) of 75 dB, a signal-to-noise ratio (SNR) of 61.5 dB, and a noise floor of –155 dBFS/Hz.A Representative Example

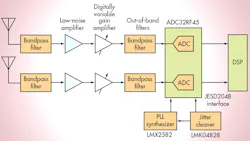

The figure shows a simplified block diagram of the ADC32RF45 used in a direct-conversion SDR receiver. The input filter selects the desired signal; the LNA amplifies it; the digitally variable gain amplifier (DVGA) ensures a proper signal input level to the ADC; and the out-of-band filter prevents aliasing. The ADC is designed to work with an external PLL synthesizer for the clock and a jitter cleaner. It connects to the DSP processor is by way of a JESD204B interface.

Among the products using the ADC32RF45 are Pentek’s FlexorSet Software Radio Modules. These modules are designed to allow engineers to build specialized communications equipment and/or experiment with different SDR designs. The modules offer two channels of ADC as well as two channels of digital-to-analog conversion (DAC). A Xilinx FPGA with internal software for data acquisition and DAC waveform generation facilitates experimentation.

Design Considerations

The most critical part of designing with the ADC32RF45 is its input circuitry. Specifically, the out-of-band aliasing filter must match the input impedance of the ADC. This is essential to ensure maximum in-band flatness of the filter and desired out-of-band rejection.

To help with this design, it’s recommended to use S (scattering) parameters. S-parameters are frequency-domain quantities involved with modeling behavior of RF circuits and components. These complex values are usually shown in a matrix format that can be manipulated to illustrate the behavior and performance of circuits and components. They’re the preferred way to design with transmission lines, filters and other high frequency devices.

The S-parameters for the ADC32RF45 are available to help in designing critical input circuitry. Furthermore, a complete reference design with an evaluation module (EVM) help speed up and simplify the design process.

Looking for parts? Go to SourceESB.

About the Author

Lou Frenzel

Technical Contributing Editor

Lou Frenzel is a Contributing Technology Editor for Electronic Design Magazine where he writes articles and the blog Communique and other online material on the wireless, networking, and communications sectors. Lou interviews executives and engineers, attends conferences, and researches multiple areas. Lou has been writing in some capacity for ED since 2000.

Lou has 25+ years experience in the electronics industry as an engineer and manager. He has held VP level positions with Heathkit, McGraw Hill, and has 9 years of college teaching experience. Lou holds a bachelor’s degree from the University of Houston and a master’s degree from the University of Maryland. He is author of 28 books on computer and electronic subjects and lives in Bulverde, TX with his wife Joan. His website is www.loufrenzel.com.

Voice Your Opinion!

To join the conversation, and become an exclusive member of Electronic Design, create an account today!

Leaders relevant to this article: