This file type includes high resolution graphics and schematics when applicable.

VPX backplanes commonly implement high-speed signal standards such as PCI Express, Serial Rapid I/O, SATA, SAS, and 10-Gbit (XAUI) Ethernet. It’s important to know that when VPX backplanes use these types of signal paths, they require point-to-point connectivity from slot to slot to maintain signal integrity and speed of communication.

Connecting multiple plug-in cards, such as CPU processor boards, graphics cards, GPU math processors, and the like via a VPX backplane can be problematic. That’s because the nature of the extremely high frequency signals used means simple “busing” between multiple card slots no longer works effectively.

High-performance, mission-critical backplanes need more flexibility to meet the wide variations in point-to-point signal-connection standards. Fabric mapping modules (ball-grid-array, or BGA, signal mapping overlays) present an effective solution with the necessary signal-integrity improvements to meet these challenges, and their use makes it possible to solve many application problems in the design phase.

From VME to VPX

Before we discuss the fabric-mapping-module (FMM) overlay techniques, let’s get more in-depth about VPX backplanes themselves. In the older VME-bus systems (the predecessor of VPX), connectors were able to accommodate parallel data buses. The VME International Trade Association (or VITA) eventually developed new standards to accommodate switched fabrics that use differential signaling at multi-gigabit speeds; this necessitated a new connector technology. The differential pairs in switched fabrics use pairs of pins that are close to one another and shielded from other signals by ground pins.

The MultiGig RT2 from Tyco was developed to meet the design requirements of VITA 46, now known as VPX. Among its most important features are quad-redundancy in pin connectivity, and the potential for electrical customization: wafers can be manufactured for differential or single-ended signal paths; and impedance, propagation delay, and crosstalk specifications can be altered as per customer requirements.

Consider some examples of backplanes that are built to accommodate the MultiGig RT. There’s a 3U VPX board with two 16-column, 7-row RT2 connectors and one 8-column, 7-row RT2 connector. And a 6U VPX board incorporates six 16-column, 7-row RT2 connectors and one 8-column, 7-row RT2 connector. VPX boards have alignment keys that also supply a safety grounding contact. The 6U board has three such keys, while the 3U has two (Fig. 1).

The density of the RT2 connector is such that when applied to a 6U board, there are 464 signaling contacts that can be allocated as follows:

• 384 differential pins that can be implemented as 192 high speed differential pairs for core fabric

• 40 single-ended pins for customer I/O

• 28 pins for system utilities

Even with the impressive performance and capabilities of the MultiGig connector, its impedance variations can create challenges when using the standard overlay techniques of circuit-board design. Printed-circuit boards (PCBs) that support high-speed signal standards, such as PCI Express, Serial Rapid I/O, SATA, SAS, and 10-Gbit Ethernet, do so by providing point-to-point direct signaling paths to maintain signal integrity. Clearly, then, multiple plug-in cards on a backplane cannot “share” a signal path, because communication no longer occurs via busing between card slots—the differential-pair nature of the connectors keeps that from being an option.

VPX Point-to-Point Signal Standards

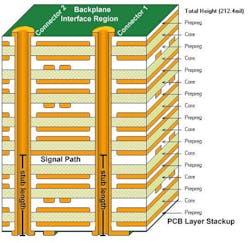

As an example, consider PCI Express generation 1. In differential-pair transmission technology, the signal from one chip’s output pairs links directly to the input pairs of the receiving chip by way of two traces that form a 100-⦠transmission line. The MultiGig VPX connector consists of small “blades” that are actually PCBs themselves, and they continue the 100- ⦠transmission line path. The connector’s “leaf-spring” contacts are designed so that any “stubs,” or short trace lengths, are as short as possible to minimize any signal reflection noise (Fig. 2).

Any stub present on a signal path will, at some frequency, cause an additional signal wave front that’s out of phase. This causes destructive interference with the original signal transmission, diminishing the signal seen by the receiving chip. The design goal is to optimize the path between the transmitting chip and receiving chip by eliminating stubs and impedance discontinuities. These factors are further enhanced by the PCI Express chip standard implementation of pre-emphasis and equalization to make the signal transmission as optimal as possible.

Another key aspect of VPX backplane design to consider is the adjacencies of the plug-in cards that go into the backplane itself. The closer the source and destination VPX cards are to each other, the faster the communication links between them. That design principle, along with the difficulties associated with balanced-pair transmission-line implementation, explains why VPX backplanes need more flexibility to meet the wide variations in point-to-point signal-connection standards. Micro-overlays that are external to the backplane itself can solve the challenge of linking these two requirements by delivering the necessary signal-integrity improvements.

Using Signal-Mapping Micro-Overlays

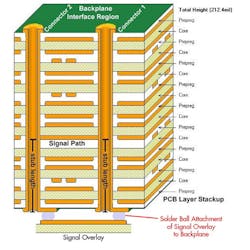

Micro-overlays use BGA solder-connection technology to interface a PCB-based differential pair matrix with compatible backplanes. They reduce transmission-line impedance variations and stubs associated with connector-based interfaces by employing two techniques:

• Stacked dielectric with alternating etched copper layers implementing signal shield plane and controlled-impedance copper-etched signal lines.

• Sub-picosecond matched signal path length. The thickness of the dielectric stackup is tuned for optimal impedance matching to the signal standard requirements. Off-signal-path stub lengths are minimized by this overlay connection technique.

These techniques improve the signal integrity between system cards beyond the requirements of PCI Express Gen 3, Serial Rapid I/O, and the 10-Gbit Ethernet standards. In addition, micro-overlays can facilitate rear transition modules and low-profile connector interface systems when normal rear transition modules don’t mechanically fit the system application (Fig. 3).

Fabric Mapping Modules For VPX Backplanes

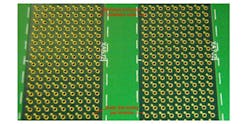

FMMs are micro-overlays that provide benefits to designers of systems incorporating VPX backplanes. Use of FMMs allows the backplanes to be semi-customized and quickly reconfigured according to user needs. Consider a backplane with power and other “utility” planes that serve multiple plug-in boards. Those planes need not change or be redesigned when a VPX-based backplane is used for a design iteration, since FMMs can be utilized to make iteration-specific changes.

With FMMs, backplane design can take a building-block approach. That’s because fundamental housekeeping planes remain the same, while board-to-board fabric changes can be accommodated simply by changing FMMs. In this way, FMMs add flexibility to the system design (Fig. 4).

One example is a primary defense contractor that needed a four-slot backplane to fit inside a conduction-cooled cube-shaped form factor meant for use in multiple vehicle types. In each case, the payload plug-in cards are different, but the power-supply plane remained the same. Processor cards and graphics cards from different manufacturers were used.

Here, the changes in plug-in cards did not require a complete redesign of the backplane. Instead, FMMs were employed, which accommodated the necessary changes on the backplane that correspond to the differences in plug-in cards and front I/O pin out.

Another example of FMM usage involves the major supplier of VPX-backplane-based deployable radio systems. The company uses processor cards, storage cards, switch cards, and radio cards that go in to different plug-in slots in the backplane, depending on the specific configuration. They rely on different FMMs to make the configuration-specific connections.

On top of that, the supplier implements connectors on the FMMs themselves to pick off signals such as Ethernet, Serial ATA, and RS-232, and then routes those signals directly to the front panel of the system. None of these changes require backplane redesigns because of the inherent flexibility derived from using FMMs.

This file type includes high resolution graphics and schematics when applicable.

In general, fabric mapping modules in high-performance, mission-critical VPX backplanes gives system designers the flexibility needed to meet the wide variations in point-to-point signal connection requirements. They also help solve many application problems in the design phase.