Lauro Rizzatti is more than one of our longest-running Contributing Technical Experts. He also was general manager of EVE-USA and its vice president of marketing before Synopsys acquired it. He also is a global citizen, whose 30-year career in the EDA and automatic test equipment (ATE) industries has spanned the globe, enabling him to reside in the United States, Europe, the Middle East, Japan, and the Pacific Rim. While cultivating an affinity for living abroad, he held management positions in product marketing, technical marketing, and engineering as well.

This file type includes high resolution graphics and schematics when applicable.

Currently a verification consultant, his impressive resume also includes leadership positions at Get2Chip (acquired by Cadence), Synopsys, Mentor Graphics, Teradyne, Alcatel, and Italtel. He has published numerous articles and technical papers in industry publications and has presented at various international technical conferences. He holds a doctorate in electronic engineering from the Universita degli Studi di Trieste in Italy and presently divides his time between the U.S. and Europe. As a hardware emulation expert, he is the ideal candidate to explain why it has become a must-have tool for chip design verification.

Wong: What is hardware emulation?

Rizzatti: Hardware emulation is a verification tool that chip designers use to debug their digital designs. It allows for the most accurate representation of the design before silicon availability since it is based on an actual silicon implementation, albeit on a by-far larger footprint. It was originally conceived in the 1980s and based on field programmable gate arrays (FPGAs). Today, emulators are based either on custom processor chips or on large FPGAs. One vendor uses commercial FPGAs. Another developed a custom FPGA.

Wong: How is hardware emulation used?

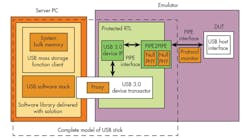

Rizzatti: Historically, hardware emulation was deployed in what is called in-circuit emulation (ICE) mode. In ICE mode, the design is mapped inside the emulator and connected to the target system where the actual silicon chip will be plugged in. This mode requires slow-down adapters between the emulator running at a few megahertz and the target system clocked at hundreds of megahertz. In recent years, a new technology called transaction-based verification has been adopted over the ICE mode. In transaction-based verification, sometimes called acceleration mode, the physical target system is replaced by a virtual target system modelled via one of the high-level languages such as SystemVerilog, SystemC, or C++. This new approach has several advantages, such as the elimination of speed adapters, no hardware dependencies, the ability to use the emulator remotely, and the ability to run verification of corner cases (Fig. 1).

Wong: Why has it become such a popular verification?

Rizzatti: The driving force of emulation is speed of execution that may be five or six orders of magnitude faster than the traditional hardware description language (HDL) simulator. The fast speed of execution not only shortens the design debug process, but it also permits users to implement real-life scenarios impossible to create with alternative solutions. Examples include processing video clips and audio files, storing/retrieving data from hard-drives or USB memory sticks, etc.

Wong: What are the benefits of using hardware emulation?

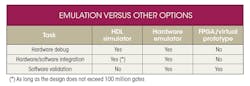

Rizzatti: The main benefit and the raison d’etre is that emulation can find any kind of design bugs, whether in the hardware or in the embedded software of a modern, complex SoC (system on chip). By contrast, HDL (hardware description language) simulators are excellent for hardware debug in the early stages of the design cycle, when the design is focused at the block level. But they run excruciatingly slow on designs of tens or hundreds of million gates. And FPGA prototypes and virtual prototypes run faster than emulators, but they do not provide the design accuracy mandatory for hardware debug, and for hardware/software integration, they excel at validation of the embedded software. Further, none other than emulation can deal with designs of several hundreds of millions of gates (see the table).

Wong: What are some of the applications?

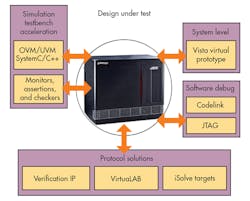

Rizzatti: There is no off-limit to the deployment of emulation. Any market segment of the semiconductor industry can benefit from emulation. It is an ideal tool for processor and graphics designs, networking, multimedia, automotive, and storage, for example. The only exceptions are analog designs since emulation requires a digital representation of the design (Fig. 2).

Wong: How does a project team go about evaluating hardware emulation?

Rizzatti: Unlike evaluating an HDL simulator, evaluating an emulator is time consuming and requires a degree of experience and expertise. Typically, the project team agrees with a vendor on an evaluation schedule that would be driven by the vendor application resources with clearly defined targets. A thorough evaluation may require several weeks.

Wong: Which companies provide hardware emulation?

Rizzatti: Large EDA companies such as Cadence Design Systems, Mentor Graphics, and Synopsys have hardware emulation solutions.

Wong: What overall trends are you seeing in verification?

Rizzatti: Certainly, emulation is here for the long run. All three vendors listed above have been reporting success after success over the last several years, and this trend will only continue. That’s due to increasingly complex and integrated designs that need thorough verification and debug resources.