AI Automation Builds Better NoCs

What you’ll learn:

- Why efficient network-on-chip (NoC) solutions are hard to build.

- How artificial intelligence is helping to improve NoC configuration.

A network-on-chip (NoC) is central to today’s system-on-chip (SoC) solutions that often incorporate GPUs and artificial-intelligence (AI) accelerators with a memory and CPU complex. Most electronic design automation (EDA) designers rarely design their own NoC from scratch.

Arteris's FlexNoC is an EDA tool for generating NoC logic to connect components on a chip based on a designer’s specification. FlexNoC handles the details while the designer defines where the connections go and what functionality is required. FlexNoC supports hard and soft tiling and AI is used to enhance the interconnect.

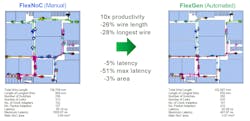

The latest enhancement is FlexGen. FlexGen provides additional automation building atop FlexNoC using AI heuristics, which the designer can customize by specifying goals. It helps optimize latency and reduce wire length and overall area (see figure).

Results from using FlexGen will vary depending on the chip components and design, but in many cases, FlexGen has improved productivity by a factor of 10 while reducing wire length by more than 25%.

Designers would use FlexNoC in an iterative fashion to design, test, and deploy NoC configurations. Beforehand, a designer needed to test each configuration manually. FlexGen does this automatically while enhancing the basic layout using AI to meet various goals that the designer can specify. Thus, the developer is able to balance size, power, performance, and latency. Scripting can be used to develop topologies, and an auto-timing closure assist addresses one of the most challenging aspects of NoC design—timing closure.

About the Author

William G. Wong

Senior Content Director - Electronic Design and Microwaves & RF

I am Editor of Electronic Design focusing on embedded, software, and systems. As Senior Content Director, I also manage Microwaves & RF and I work with a great team of editors to provide engineers, programmers, developers and technical managers with interesting and useful articles and videos on a regular basis. Check out our free newsletters to see the latest content.

You can send press releases for new products for possible coverage on the website. I am also interested in receiving contributed articles for publishing on our website. Use our template and send to me along with a signed release form.

Check out my blog, AltEmbedded on Electronic Design, as well as his latest articles on this site that are listed below.

You can visit my social media via these links:

- AltEmbedded on Electronic Design

- Bill Wong on Facebook

- @AltEmbedded on Twitter

- Bill Wong on LinkedIn

I earned a Bachelor of Electrical Engineering at the Georgia Institute of Technology and a Masters in Computer Science from Rutgers University. I still do a bit of programming using everything from C and C++ to Rust and Ada/SPARK. I do a bit of PHP programming for Drupal websites. I have posted a few Drupal modules.

I still get a hand on software and electronic hardware. Some of this can be found on our Kit Close-Up video series. You can also see me on many of our TechXchange Talk videos. I am interested in a range of projects from robotics to artificial intelligence.

Voice Your Opinion!

To join the conversation, and become an exclusive member of Electronic Design, create an account today!

Leaders relevant to this article: