In the first installment, five basic designs, utilizing four EPC2001 (100 V, 25 A) paralleled devices per switch, in a half-bridge configuration are presented. The merits and drawbacks of each of the parametric factors are discussed. In the second installment, a 1MHz Buck Converter is demonstrated using paralleled eGaN FETs with exceptional performance, compared with state-of-the-art silicon devices in a similar circuit.

In this two-part article, we consistently define a “switch” as the paralleled group of FETs acting as a single transistor. The paralleling of eGaN FETs will furthermore be limited to a single gate driver per switch.

Paralleling Considerations

To successfully parallel eGaN FETs, one needs to understand all the parameters and their interactions. The main areas to consider are; (1) Device characteristics and (2) Circuit Parameters.

Enhancement mode Gallium Nitride (eGaN) is relatively new technology and therefore, device characteristics need to be studied for their possible effect on paralleling compatibility.

Most notable are the following:

- Selection of devices to parallel: e.g. multiple small devices verses fewer large devices

- Do the devices have a positive or negative temperature coefficient of key characteristics such as RDS(ON) or Vth?

- How do part-to-part and lot-to-lot variations affect the design?

An eGaN FET’s RDS(ON) exhibits a positive temperature coefficient that helps with paralleling. When one device in a switch gets hotter than its counterparts, it will begin to increase its RDS(ON) and as such carry less of the total current burden. This allows it to cool until equilibrium between all the devices is reached.

Whereas eGaN FETs have a threshold voltage (Vth) with a slightly positive temperature coefficient, variations in Vth can manifest as a shift in time at which a device will turn on and off with respect to the other devices. These time shifts can lead to a single device having to carry the total load burden for a short period of time. In addition, these shifts can induce unwanted current-induced voltages across inductances located between the devices. In extreme cases this can lead to false turn-on or turn-off triggering with disastrous consequences for the switch. Detailed analysis of eGaN FETs show that variations in timing resulting from Vth variations are extremely small compared to the switching transient times. As an example: using a total gate rise time of 8 ns (from 0 V to 5 V) with two devices connected in parallel, one having a Vth = 1.4 V and the other Vth = 1.54 V, leads to a time shift of only 224 ps, which translates into < 5% of the total drain-source switching transition time. This issue is discussed in more detail in [7].

Circuit Parameters

eGaN FETs, just as their MOSFET counterparts, cannot simply have each of their respective terminals connected to each other to yield a good switch. Certain circuit changes are needed to ensure maximum performance from each of the devices and that the paralleled switch can function at near theoretical maximum performance. In addition, eGaN FETs switch faster, have a lower threshold voltage (Vth) and may have a higher miller capacitance ratio, all of which will force the designer to pay particular attention to the parallel layout design and resultant circuit.

Fig. 1. shows a generic schematic for a half-bridge converter with details of the lower switch having two devices connected in parallel. There are two parameters that need to be controlled in the circuit to ensure reliable operation: (1) Source inductance which can induce unwanted gate voltages into a device and is dependent on the di/dt of the current flowing through the switch, and, (2) Miller capacitances which can induce a current into the gate path during switching events and is driven by the dv/dt of the switch. Ironically, to ensure that di/dt does not induce gate voltages requires a high impedance gate loop while at the same time low impedance in the gate loop is needed to minimize the effect of dv/dt induced gate currents. This is shown in detail in Fig. 2 and the accompanying paragraph{13}.

To overcome this design contradiction, one must understand the impact of each of these effects: how much can be tolerated, and what else can be done to mitigate the problems they may cause. Ultimately, the design comes down to how well the gate drive circuit can be isolated from the power circuit through design.

Detailed analysis and simulations reveal the following:

- The source inductance is the most important element in the circuit and must be kept as low as possible. Drain inductance may be sacrificed to achieve this.

- The gate inductance will be higher than the source inductance and it will be very difficult to get it below a ratio of 10:1. This is due to the narrow width and length of the gate drive transmission line.

- The gate driver source and sink impedance can be “programmed” to further improve switching performance by means of dv/dt reduction but this will come at the expense of efficiency.

- A complete solution, including gate inductance, results in a third order system with both sinusoidal and exponential terms that require a numerical analysis for a solution.

Fig. 2. shows the simplified circuit for the gate loops with the circuit elements that can affect the dv/dt and di/dt immunity of the switch. The dv/dt circuit simplifies down to a current divider and the di/dt circuit to that of a voltage divider. Making certain simplifying assumptions, one can derive the resultant equations for di/dt and dv/dt immunity for the switch. These equations will work equally well for a single device or for multiple paralleled device switch. The key is to identify the correct source and gate loop inductances when using the equations.

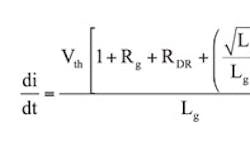

The di/dt immunity for the switch can be determined using.:

Where:

di/dt = Rate of Change in current through source inductor [A•s-1]

Vth = Threshold Voltage of switch [V]

Rg = Gate Resistance [Ω]

RDR = Gate Driver output Resistance [Ω]

Lg = Gate Inductance [H]

Cgs = Gate-Source Capacitance [F]

Ls = Source Inductance [H]

The dv/dt immunity for the switch can be determined using:

Where:

dv/dt = Rate of Change in voltage across drain-source [V·s-1]

Cgd = Gate-Drain Capacitance [F]

egan fets VS. MOSFETs

Both the actual device parameters and the component layout parameters become important when it comes to paralleling devices [5]. As an example, consider a simplified switching circuit with Lg neglected and the drain current increases linearly during the entire commutation time. The current commutation interval can then be approximated by:

Where:

t∆I = Current commutation interval time [s]

gm = Trans conductance [S]

VDR = Gate Driver voltage [V]

IDS = Drain Current [A]

Since eGaN FETs have lower drive voltage capability, gate resistance and capacitances than an equivalent MOSFET, the effect of the common source inductance term in the above equation becomes much more pronounced. The above current commutation time equation is plotted for varying values of common source inductance for the EPC2001 FET and an equivalent state-of-the-art MOSFET [Infineon BSC060N10N] in Fig. 3 for both turn-on and turn-off intervals (for turn-off, the term VDR - Vth is replaced by Vth). It clearly shows that the eGaN FET commutation time is much more affected by common source inductance than the MOSFET, which can actually exceed the eGaN FET performance for high enough values of Ls.

Similarly, the voltage commutation interval can be considered in two ways. Firstly, determining the maximum switching time capability of a given gate driver and, secondly, determining the susceptibility to false turn-on due to such an induced dv/dt event.

Where:

t∆V = Voltage commutation interval time [s]

Qgd = Gate-Drain charge [C]

RDR-up = Gate Driver turn-on resistance [Ω]

VPL = Plateau voltage [V]

If we now assume a peak dv/dt during this transition is roughly 30% higher than the average dv/dt, then the absolute minimum switching time without a dv/dt (Miller) turn-on event can be approximated by:

Where:

t∆Vimmune = Voltage commutation interval time for immunity [s]

VDC = DC Bus voltage [V]

RDR-down = Gate Driver turn-off resistance [Ω]

The resultant dv/dt commutation times are plotted as function of gate drive resistance Rg and shown in Fig. 4. Also plotted in Fig. 4 is the limit of the commutation time before the Vth for the FET is exceeded. This commutation time is defined as the immunity limit for the complimentary switch, and switching any faster can lead to unwanted switching behavior. It can be seen in Equation (4) that in the case of a MOSFET, the commutation times are much higher than those predicted for immunity, providing higher dv/dt immunity. In the case of the eGaN FET, the commutation time for immunity is higher than what can be achieved; hence lower values of Rg for turn-off are recommended than for turn-on.

From the graph in Fig. 4, it can further be seen that, because the eGaN FET can switch faster than a MOSFET, and due to its smaller charge, it is less sensitive to changes in Rg. This does not however, imply greater immunity for the eGaN FETs.

With more devices connected in parallel, the contribution of Lg, and RDR will increase as the gate loop gets longer, so dv/dt immunity will suffer, leaving the only option to improve the immunity is to increase switching time.

Layout

The eGaN FET Line Grid Array (LGA) package [6] is a dramatic and positive departure from traditional MOSFET packaging. The LGA package helps drive new layout designs that yield significant reduction in parasitic inductances between devices connected in parallel. Given that the eGaN FETs switch very rapidly and have a low gate threshold voltage, these new options are critically important to achieving the best possible solution to paralleling the devices. Despite the advantages provided by the eGaN package and device, designers still need to pay careful attention to the layout of a converter design.

Layout designs are always required to be addressed from two angles: (1) printed circuit board restrictions (including board populating) and (2) placement and routing design. eGaN FETs are no exception to this requirement, but may require additional thought due to their small size, compact connection structure, and high demand on specifications such as current and voltage.

To answer the many questions on layout, EPC developed five half bridge designs with up to four devices per switch connected in parallel (Fig. 5.). The block diagram of the test setup is shown in Fig. 6.

The difference between each of the designs is summarized in Table 1. The definitions of the gate structures used in Table 1 are shown in Fig. 7.

Analysis and measurements of the five designs yield gate and source inductances given in Table 2.

Paralleled Switch di/dt Immunity

The inductance values can now be used to determine the di/dt limits of operation for each of the designs. These numbers can then be used to determine which design yields the best possible operation for paralleling. Subsequently the number of devices for a design can then be varied from one through four devices in parallel to determine a parallel impact figure for eGaN FETs.

The source inductance is largely shared in the gate loop causing voltages to be induced that can lead to undesired turn-on or turn-off of a switch. The amount of voltage induced into the gate by the common source inductance during a di/dt event is given by Equation 1.

Setting a limit of induced voltage as the gate threshold voltage (In the case of the EPC2001 device this limit is typically 1.4 V [6]) one can determine the di/dt limit for a design.

Using the inductance values from the table and the typical threshold voltage reveals the di/dt limits for each of the designs when using four devices as shown in Table 3.

It can be seen from the di/dt immunity results that design A is far inferior in performance to any of the other designs. This design was included to emphasize the incorrect method to parallel eGaN FETs and is a method that may otherwise seem attractive because it produces a very low supply loop decoupling inductance.

Paralleled Switch dv/dt Immunity

Now that di/dt immunity has been addressed, the dv/dt immunity must also be considered. The rapid voltage transition across the drain source can induce a current into the gate circuit. This occurs when the switch is turned off and the opposite switch is turned on. A low gate impedance that includes the gate driver will ensure that the gates of the devices in the switch remain off during a dv/dt event. From Fig. 1 and Fig. 2 it can be seen that there are several elements in the gate circuit that include:

- Turn-off resistance (Rgoff)

- Gate circuit inductance (Lg)

- Common Source inductance (Ls)

- Gate-Source capacitance (Cgs)

- Gate-drain capacitance (Cgd)

- Gate driver off state resistance (RDR) (embedded in Vgatedrive)

Analysis of the gate circuit reveals that the inductances and resistance all connect in series across the gate. Cgd will be the component that induces the current into the gate, and the impedance of the elements in the gate circuit will determine the voltage rise. Cgd is nonlinear with respect to drain voltage and therefore the analysis can get complicated. As a simplification, a fixed value of 60 pF is used for this analysis. For the evaluation boards the following values of resistance were used RDR = 100 mΩ and Rgoff =1 Ω.

It can be seen that the trace resistance will become negligible since the trace was kept very short. The circuit reduces to the series combination of the resistances (Rg +RDR) and inductances (Lg + Ls) across Cgs. The induced current will divide between Cgs and the resistance-inductance circuit. This circuit can be complex to solve for dv/dt as some solutions have oscillatory components. Suffice to state that the resistances (Rg +RDR) and inductances (Lg + Ls) should be kept as low as possible. For all the designs the resistances (Rg +RDR) are the same it can therefore be concluded that the level of immunity is inversely proportional to the inductances (Lg + Ls). Table 4 has the calculated results.

Switching parallel impact figure

Converter performance, whether designed using a single device or with multiple devices connected in parallel can be quantitatively compared by creating a meaningful parallel impact figure (PIM). This figure of merit only encompasses switching capability and the obvious RDSon and thermal benefits are omitted. dv/dt and di/dt immunity has been shown to be a key performance consideration; thus, it is logical to include these quantities to define PIM for predicting parallel device converter performance.

Where:

dvn//dt = dv/dt immunity for n number of devices connected in parallel [V•s-1]

din/dt = di/dt immunity for n number of devices connected in parallel [A•s-1]

dv1//dt = dv/dt immunity for a single device version of the converter [V•s-1]

di1/dt = di/dt immunity for a single device version of the converter [A•s-1]

n = Number of devices connected in parallel per switch

Using Equation 7 and normalizing to a single device version of the designs yields the graph of normalized PIM for each of the two and four paralleled FET designs (Fig. 8). Table 5 gives the inductance and immunity limits. Fig. 10. shows the PIM.

From the PIM results it is clear that design B is the best design. We can now study this design in more detail to determine how the number of paralleled devices will affect converter performance. Fig. 9 shows the variations of layout for design B with varying devices connected in parallel.

References

- Eliminating Parasitic Oscillation between Parallel MOSFETs, Jonathan Dodge, Advanced Power Technology Application note APT-0402 Rev A, March 25, 2004

- Circuits and Methods for Failure Prediction of Paralleled MOSFETS, US7330046, February 12, 2008

- Paralleling Of Power MOSFETs For Higher Power Output, James B. Forsythe

- Limiting Cross-Conduction Current in Synchronous Buck Converter Designs, Alan Elbanhawy, Fairchild Semiconductor Application note AN-7019, September 30, 2005

- Analytical Loss Model of Power MOSFET,î Yuancheng Ren, Ming Xu, Jinghai Zhou and Fred C. Lee, IEEE Transactions on Power Electronics Vol.2 No.2 March 2006

- EPC2001 - Enhancement Mode Power Transistor, Efficient Power Conversion datasheet for EPC2001

- Impact of Rise Time Driving Signal and Mismatch Threshold Voltage MOSFETís in Parallel Connection of Push-Pull Power Inverter, Myzafere Limani, Qamil Kabashi, Nebi Caka, Milaim Zabeli, International Journal of Circuits, Systems and Signal Processing, Issue 1, Volume 5, 2011

- Get 600 Watts RF from Four Power FETs, Helga Grasberg, Motorola Semiconductor Engineering bulletin EB104/D

- Analysis of Avalanche Behaviour for Paralleled MOSFETs, Jingdong Chen, Scott Downer and Anthony Murray and David Divins, SAE World Congress 2004

- Parallel Operation Of Semiconductor Switches, Fairchild Semiconductor Application note AN-7513

- Paralleling HEXFET® Power MOSFETs, International Rectifier Application Note AN-941

- Paralleling Power MOSFETs in Their Active Region: Extended Range of Passively Forced Current Sharing, Janis M. Niedra, NASA Contractor Report 180902, July 1989

- The eGaNTM FET-Silicon Power Shoot-Out: 2: Drivers, Layout, Johan Strydom, Power Electronics Technology, January 201, pp 14-19