Multicore RISC-V Designs for Smart Automotive Apps

What you’ll learn:

- How MIPS supports functional safety with RISC-V.

- What functionality is provided by MIPS RISC-V P8700 core?

- Why designers are looking to vendors like MIPS for solutions rather than the core IP.

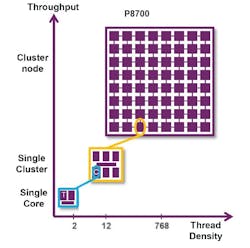

The rise of RISC-V has been rapid, but adoption within safety- and security-critical spaces requires implementations that can meet requirements like ISO 26262 and ASIL B/D. In the video above, I talk with Sameer Wasson, CEO at MIPS, about the company’s “very MIPSy core,” the P8700 RISC-V core (Fig. 1).

The P8700 supports the RISC-V RV64GC instruction set architecture (ISA). The out-of-order (OOO), non-blocking execution unit includes an 8-wide instruction fetch with a 4-wide decode unit and a 7-wide issue queue. The core design maintains multi-cluster support along with PDtrace hybrid debug support.

Six of the P8700s fit into a cluster, and the implementation can be replicated up to 64 times to support 768 execution threads (Fig. 2). The cores have a 48-bit physical address space.

The MIPS Coherence Manager and shared virtual memory (SVM) use an AMBA ACE interface to tie the RISC-V clusters and the I/O coherence unit (IOCU). The manager supports up to eight units, which usually translates to six RISC-V cores and two IOCUs. The IOCU ports are optimized for low latency.

On the functional-safety side, the P8700 includes a fault bus that can be tied to external fault-handling logic. Parity is supported on all address and data buses. It’s also applied to software visible registers like the interrupt controller, cluster power controller (CPC) blocks, and global configuration registers (GCRs). Tag and data arrays provide ECC support.

>>Check out more of our CES 2025 coverage, as well as this TechXchange for similar articles and videos

About the Author

William G. Wong

Senior Content Director - Electronic Design and Microwaves & RF

I am Editor of Electronic Design focusing on embedded, software, and systems. As Senior Content Director, I also manage Microwaves & RF and I work with a great team of editors to provide engineers, programmers, developers and technical managers with interesting and useful articles and videos on a regular basis. Check out our free newsletters to see the latest content.

You can send press releases for new products for possible coverage on the website. I am also interested in receiving contributed articles for publishing on our website. Use our template and send to me along with a signed release form.

Check out my blog, AltEmbedded on Electronic Design, as well as his latest articles on this site that are listed below.

You can visit my social media via these links:

- AltEmbedded on Electronic Design

- Bill Wong on Facebook

- @AltEmbedded on Twitter

- Bill Wong on LinkedIn

I earned a Bachelor of Electrical Engineering at the Georgia Institute of Technology and a Masters in Computer Science from Rutgers University. I still do a bit of programming using everything from C and C++ to Rust and Ada/SPARK. I do a bit of PHP programming for Drupal websites. I have posted a few Drupal modules.

I still get a hand on software and electronic hardware. Some of this can be found on our Kit Close-Up video series. You can also see me on many of our TechXchange Talk videos. I am interested in a range of projects from robotics to artificial intelligence.