Arteris FlexNoC is a Network-on-Chip (NoC) interconnect designed for building high-performance System-on-Chip (SoC) platforms. The use of a third-party NoC interconnect can reduce time to market and result in smaller die sizes that in turn reduces cost. The modular design makes derivative chip design easier as well. It can handle a range of architectures including AXI, OCP, and AHB in addition to proprietary interfaces.

The new FlexNoC Physical product is designed for automated timing closure with FlexNoC designs. It can save as much as three months of work due to timing closures on complex SoC designs (Fig. 1). This in turn reduces the cost of the SoC.

The challenges addressed by FlexNoC Physical are significant because of the tight timing requirements on today’s SoCs. These are often so large that signals cannot move from one side of the SoC to the other in one clock cycle. These designs require timing pipelines to latch data as required by the system timing specifications.

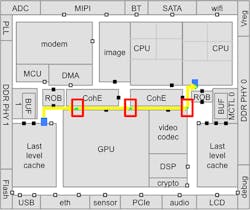

FlexNoC Physical adds timing pipelines automatically as necessary for a given design (Fig. 2). In the past these adjustments were done manually. The auto-pipe approach allows the SoC floorplan to be done early in the design cycle with the NoC timing handled independent of the modules it connects. It also provides a finer-grain implementation because the system does not care how many auto pipes are used or where they are incorporated.

The reason Arteris’ approach is important is because not all SoC designs are possible. There have been a number of large SoC designs that had to be scrapped because the timing requirements could not be met. This was not determined until after all the systems were integrated, because the timing closure was done last.

FlexNoC Physical allows the NoC timing to be locked down early in the design cycle. The final FlexNoC layout with a workable timing closure will allow the final SoC design to be workable (Fig. 3).