Lower-Power, Cost-Optimized Flash FPGAs Can Handle 40 Gbit/s Ethernet Chores

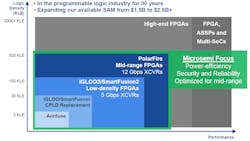

1. Microsemiâs new PolarFire FPGA family takes on mid-range RAM-based FPGAs in terms of performance while delivering low-cost, power-optimized solutions.

Microsemi’s flash-based FPGAs have been well known in the embedded space where low power and high reliability is required. Its flash architecture provides instant-on operation versus RAM-based FPGAs, and also makes it more rad-tolerant than RAM-based FPGAs. The firm has been on the forefront when it comes to securing its chips.

Microsemi has had a range of FPGAs, from its tiny 3-mm by 3-mm Igloo (see “FPGA Costs Half A Buck” on electronicdesign.com) through the SmartFusion 2 with integrated Cortex-M3 hard cores to its rad-tolerant series.

Most of these solutions tended to address the low end of the FPGA space. Its new PolarFire series moves Microsemi up a notch with a line that addresses the midrange where high logic capacity and high performance are needed (Fig. 1). For example, PolarFire has 12.7 Gbit/s SERDES transceivers that can handle chores like 40 Gbit/s Ethernet. It is leaving the higher-end 100 Gbit/s Ethernet to the RAM-based FPGAs for now, but this is a rarified space for enterprise and cloud services, in addition to military and avionic applications where cost and power requirements are less of an issue compared to performance and capacity.

PolarFire hits the sweet spot of 1G to 40G that is very popular today. The family supports up to 500 KLE (thousands of logic elements), making it significantly larger than the Igloo2 and SmartFusion 2 series that currently top out at about 150 KLE (Fig. 2).

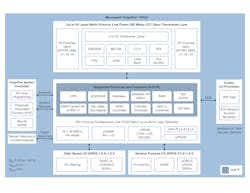

2. The PolarFire family supports up to 500 KLE, more than three times the size of the Igloo2 and SmartFusion 2 series.

The PolarFire family can host up to 24 12.7 Gbit/s SERDES lanes (Fig. 3) that support standard interfaces like Ethernet as well as PCI Express. The crypto support includes a true hardware random number generator (RNG) with differential power analysis (DPA) prevention support and physically unclonable function (PUF) support.

The flash-based FPGA logic cells use a single event upset (SEU) immune configuration that is useful in general and invaluable for rad-hard solutions. It has a range of high speed and general I/O interfaces along with high- and mid-speed DRAM interfaces. The 1.6 Gbit/s I/Os include SGMII support.

SEU is not the only high-reliability technology employed in PolarFire. It also has single-error correcting and double-error detecting (SECDED) support on internal memories.

3. The PolarFire family supports up to 24 12.7 Gbit/s SERDES, multichannel RAM interfaces along with crypto support.

Microsemi’s Libero IDE provides access to a wide range of Soft IP, including Common Public Radio Interface (CPRI), JESD204B for analog interfaces, Interlaken, Ethernet, SATA, and memory controllers. Microsemi also makes the soft core ARM Cortex-M1 available to developers along with the emerging RISC-V architecture.

The use of flash memory has a number of additional advantages, including very low static power compared to RAM-based FPGAs. This can be the difference between a fan and heatsink or no heatsink. Flash-based solutions have minimal start-up power requirements, whereas RAM-based solutions have high current requirements at that time. Finally, there is Microsemi’s Flash*Freeze mode that maintains SRAM, registers, and interface data while cutting power consumption to microwatts.

4. The initial part will be the MPF300 with 300 KLE, 512 I/O and 16 12.7 Gbit/s SERDES.

The initial part will be the MPF300 with 300 KLE (Fig. 4). It will be available in a 16-mm by 16-mm package with 120 high-speed I/Os, 180 GPIOs, and 4 SERDES. Larger packages increase the number of interfaces.

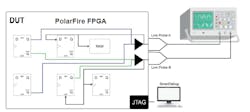

PolarFire designers needed a way to debug their FPGAs and wound up with a diagnostic tool that is needed for the production and testing of the parts. It turns out to be valuable debugging tool in general called SmartDebug (Fig. 5).

SmartDebug provides access to two points within the FPGA. These can be changed without recompiling and reprogramming the FPGA. Normally debug logic needs to be compiled as part of the system. This type of support can be used in addition to SmartDebug.

The PolarFire Debug Kit (Fig. 6) will be available mid-year. It includes an FMC socket and a QSFP+ connector. The lower-cost PolarFire Splash Kit will be out in Q3. Both are supported by PolarFire’s Libre IDE.

6. The PolarFire Debug Kit will be available later this year.

PolarFire represents a major change for Microsemi. It now has a product line that spans the major application areas with the exception of the very-high-end, high-speed, and high-cost arena. Its flash-based FPGA has major power and reliability advantages that make many FPGA applications viable, including mobile solutions.