AI-Enabled RISC-V Cores Target ASIL B Automotive Apps

What you'll learn:

- Why ASIL B capabilities are critical to RISC-V adoption.

- How AI acceleration can be incorporated into the MIPS P8700 core.

Arm has dominated the automotive safety-related arena with its Cortex-M and Cortex-A families. RISC-V vendors have been able to make inroads in other aspects of the car and now they can address areas that require ASIL B(D) and ISO 26262 functional-safety certification with the MIPS P8700 core.

To meet these requirements, the design includes fault-detection capabilities such as end-to-end parity protection on address and data buses as well as software-visible registers. The cores incorporate a fault bus for reporting errors within a system.

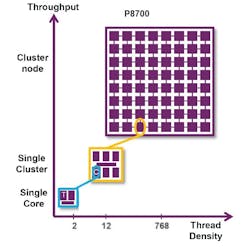

The P8700 (Fig. 1) implements the RISC-V RV64GC instruction set architecture (ISA). Its cluster architecture is based on half-a-dozen 64-bit cores with a shared L2 cache. Each core can support one or two threads with a shared L1 cache, too. The cores support a 48-bit virtual and physical memory space. The out-of-order (OOO) execution system employs an 8-wide instruction fetch feeding a 4-wide decode and a 7-wide issue queue with rename and graduation support.

Up to 64 clusters can be built into a system-on-chip (SoC), which translates to 768 threads. Clusters are tied together using MIPS Coherence Manager with an AMBA ACE interface (Fig. 2). Each core can be configured with different combinations of cache and threads. The I/O coherence unit (IOCU) ports are optimized for low-latency connection with accelerators using shared virtual memory (SVM).

The cores alone can be utilized for artificial-intelligence and machine-learning (AI/ML) processing. The IOCU support allows clusters to be combined with AI/ML accelerators for even more powerful and power-efficient AI/ML solutions.