Cortex-M7 Contains Configurable Tightly Coupled Memory

This file type includes high resolution graphics and schematics when applicable.

Atmel’s SAM E70 now adds Cortex-M7 (see “Cortex-M7 Takes Aim at the IoT High Ground”) support to its ARM product portfolio. The Cortex-M7, which features high-performance floating-point capability, is the high end of the ARM architecture microcontroller line, yet it also bumps into the low-end, Cortex-A5 application-processor range.

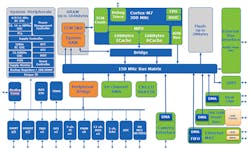

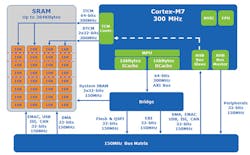

The SAM E70 is built around a 300-MHz Cortex-M7 with dual 16-kB L1 caches and up to 2 MB of on-chip flash storage (Fig. 1). A 150-MHz bus matrix links the processing core, two dozen direct-memory-access (DMA) channels, and memory controllers to on-chip storage. The processor caches work with the on-chip and off-chip storage, including the QSPI port, although deterministic code should be loaded into RAM for optimal operation.

Its aggressive tightly coupled memory (TCM) design with four ports maximizes throughput and minimizes latency for the processor and DMA (Fig. 2). It provides single-cycle access to bus masters and is designed for consecutive, burst-mode transfers that occur with caches and DMA. Access is prioritized with the processor fixed at level 2 of four. The processor has 64-bit access using two ports, while devices have 32-bit access using a single port.

The TCM divides into instruction (ITCM), data (DTCM), and system memory (System SRAM). The amount for each is configurable; for example, ITCM could be increased to allow for more hard real-time code like motor control or audio-processing code. More System SRAM might be needed for communication protocol stacks.

The chip includes Ethernet support with MI/RMII interfaces, USB High Speed (HS) support with on-chip PHY, a camera interface, dual CAN, and QSPI interfaces. For security, there’s a hardware random number generator (RNG) and AES 256-bit encryption support. It includes a host of timer and serial interface ports as well as dual 12-channel, 12-bit, 2-Msample/s ADCs and dual 12-bit, 2-Msample/s DACs.

The SAM E70 has a number of wakeup methods, including an address recognition system that’s part of the I2Cinterface. The interface can operate when the processor and other peripherals are asleep, reducing power requirements. It uses its own clock and tracks incoming data, waking up only when the matching address is recognized.

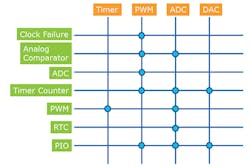

Atmel has included an event crossbar system (Fig. 3). This allows for cross-triggering of peripherals based on selected events. The peripherals can operate when the processor is asleep and without processor intervention. This reduces processor overhead, enabling the system to do more with less power.

This file type includes high resolution graphics and schematics when applicable.

Atmel provides a range of tools and software support in addition to an active third-party environment, including RTOS support from Express Logic (Thread-X), Segger (embOS), FreeRTOS, Nuttx, and ARM (RTX). The ATSAMV71-XULT Xplained development board is available. The company includes open-source middleware for the USB devices, Ethernet, flash file storage, and a JPEG encode/decode. Automotive versions are available as well.