Dynamically Reconfigurable Processors Accelerate Machine-Learning Apps

What you’ll learn:

- What is a dynamically reconfigurable processor (DRP)?

- How DRPs accelerate machine-learning applications.

- Why is the RZ/V2H well-suited for robotic apps?

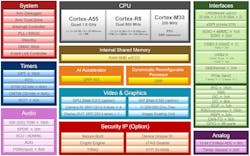

Renesas's RZ/V2H system-on-chip (SoC) is the latest high-end platform in the company’s RZ family (Fig. 1). It targets applications that need application processors, including four, 1.8-GHz Arm Cortex-A55 cores as well as dual, 800-MHz Cortex-R8 and a Cortex-M33 real-time cores. Display capabilities are supported via an Arm Mali-G31 GPU along with a Mali-C55 image signal processor (ISP). Its graphic and camera support allow it to handle a range of embedded applications, such as those in the automotive space.

The RZ/V2H (Fig. 2) provides a balanced set of features. Among them are communication interfaces, security, plus analog and streaming video support that are well-suited for applications like robotics, which use machine vision requiring artificial-intelligence and machine-learning (AI/ML) support.

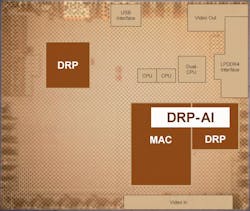

The RZ/V2H targets AI/ML applications with its dual dynamically reconfigurable processors (DRPs) and DRP-AI support. The latter is a combination of a DRP and multiply/accumulate (MAC) unit (Fig. 3). This differs from the competition that often employs a dedicated neural processing unit (NPU), which tends to be optimized for a particular class of AI/ML models. The DRP provides more flexibility—for example, the ability to address different types of processing. This includes support for OpenCV machine-vision applications.

The SoC’s DRP-AI capability can deliver better power efficiency up to 10X using a number of enhancements (Fig. 4). Moving to INT8 weights, instead of FP16 floating point, provides a more compact representation while maintaining comparable accuracy, and it cuts storage requirements in half.

The use of unstructured pruning by the compiler eliminates many unnecessary operations and data from the model. Some applications can see even more performance and efficiency improvements. This allows for real-time implementation of many inference models while eliminating the need for heatsinks.

The second DRP for vision processing chores is a good complement to the streaming video inputs. By supporting the OpenCV standard, it can handle applications that utilize the standard API. It manages visual inspection chores as well as robotic applications that utilize visual simultaneous localization and mapping (vSLAM) technology (Fig. 5).

An RZ/V2H evaluation kit features an additional 8 GB of LPDDR memory and 64 MB of SPI flash memory. Also in the mix is a pair of MicroSD sockets. Moreover, the system exposes the other SoC interfaces, including dual Gigabit Ethernet, dual USB 3.2 Gen 2, dual USB 2.0, x4 PCIe Gen 3, four MIPI CSI-2 camera interfaces, and a MIPI-DSI display interface. The expansion board, which provides HDMI and audio interfaces, has four PMod connectors.