16-nm FPGA Includes 64-bit and Lockstep ARM Cortex Cores

Xilinx's latest FPGAs move down to 16-nm. This includes the latest Virtex UltraSCALE+ and Kintex UltraSCALE+. The Zynq line (see “FPGA Packs In Dual Cortex-A9 Micro”) gains a big brother with the Zynq MPSoC version that includes a multicore Cortex-A53 and Cortex-R5 complement plus a Mali GPU. These are built on TSMC's 16FF+ FinFET 3D transistor technology. The UltraSCALE line now spans 16- and 20-nm. It provides a 2x to 5x improvement compared to the 28-nm FPGAs from Xilinx.

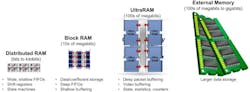

There are a few architectural improvements in addition to higher performance and lower power requirements. One of these improvements is UltraRAM (Fig. 1). UltraRAM fills the gap between the conventional distributed and block RAM found in FPGAs and external memory. It is configurable like these other two RAMs, but with capacity in the hundreds of megabits. This makes it ideal for video and packet buffering as well as counters and other application statistics. In the past, many applications used slower, less efficient external memory that only used a fraction of the capacity. Virtex UltraSCALE+ FPGAs will be available with up to 432 Mbits (54 Mbytes) of UltraRAM.

Xilinx is also highlighting the high-end Virtex chips as 3D-on-3D technology. This includes the TSMC 3D FinFET transistor technology and Xilinx's interposer technology to mix silicon chips (see “10,000 Connections Between FPGA Slices”). Xilinx had highlighted this as 2.5D technology, but 3D looks so much better. This interposer technology essentially provides a silicon circuit-board interconnect between FPGA slices. Xilinx typically uses this to incorporate very high-speed SERDES as well as expanding the size of the FPGA fabric. Thousands of connections are made between the slices. It does have a 3D structure, although it is not full 3D stacking like that used with Samsung's 3D V-NAND flash memory that stacks multiple layers of silicon ( see “The Changing Face Of Non-Volatile Storage”).

SmartConnect is a new feature introduced with UltraSCALE+, but it is a software technology incorporated into Xilinx's Vivado development tool.

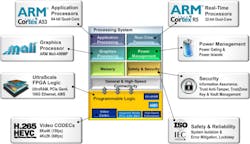

One of the biggest changes is the addition of the Zynq MPSoC to the Zinq series. The original dual-core Cortex-A9 versions are still available, but they are blown away in terms of performance by the MPSoC's 64-bit, quad-core Cortex-A53 and a 32-bit, dual-core Cortex-R5 (Fig. 2). It is a complete ARM-based SoC with a Mali-400MP GPU and TrustZone security that includes key and vault management. The SoC has its own memory, so it does not have to use UltraRAM to operate. There are hard PCI Express blocks and a H.2fs65 HEVC (high efficiency video coding) CODEC.

The Zynq MPSoC is designed to take on Altera's quad-core Cortex-A53 FPGAs (see “FPGA Embeds 64-bit Cores and High-Speed Interfaces”). Xilinx's inclusion of the Cortex-R5 allows more real-time software support and the GPU makes display chores easier to handle. The Cortex-R5 cores can be configured to operate in lock-step mode to address safety and high reliability applications. The chips are designed to address IEC61508 and ISO 26262 functional safety standards.

The Zynq MPSoC is designed to be power-efficient in addition to delivering high performance. It supports power gating and it is divided into numerous, controllable, power islands.

Overall, the UltraSCALE+ is an impressive move forward for Xilinx. While the performance and efficiency gains are significant, it's the Zynq MPSoC that stands out. There are no half measures here, and the SoC now has the horsepower to take advantage of the new FPGA fabric.