Hyper-Registers Boost Throughput in Monolithic FPGA Chip

Altera’s Stratix 10 (Fig. 1) is its top-of-the-line FPGA, built using Intel’s 14 nm Tri-Gate 3D transistor technology. It incorporates a host of new technologies designed to deliver twice the performance in a more secure fashion while using less power per function.

The Intel connection is not surprising given Altera’s and Intel’s previous work such as the Intel E600C system-on-chip (see “Configurable Platform Blends FPGA with Atom”). It packed a 40-nm Altera Arria II FPGA with an Intel Atom core into a 37.5 mm × 37.5 mm BGA package. And now, of course, Altera is going to be inside Intel (see “Intel Really Set to Buy Altera FPGAs”) if everything pans out.

Stratix 10 can be delivered with more than 5.5 million logic elements (LEs) or adaptive logic modules (ALMs) in Altera-speak. This monolithic chip can deliver 10 TFLOPS of computation using hard DSP blocks and its interfaces can deliver 1.2 Tbits/s.

One way for Altera to hike performance was to spin the high-speed interfaces onto separate silicon tiles. The 3D System-in-Package (SiP) uses an embedded multi-die interconnect bridge (EMIB) similar to silicon interposers that also uses through-silicon vias (TSVs). TSV technology has been used in other FPGAs (see “10,000 Connections Between FPGA Slices”) and ASICs. It tends to be used in larger chips and ones where different technologies are needed. Multichip packages are another alternative.

EMIB is a bit different than the standard silicon interposer since it does not span all the chips it connects. Instead it is a small link between adjacent chips. This costs less and provides shorter, faster connections. The approach allows Altera to utilize 144 SERDES operating at speeds up to 30 Gbits/s. The approach is not limited to a particular SERDES. Look for future tiles with Ethernet, PCIe Gen 4, 56 Gbit/s, PAM-4, and optical transceiver technologies.

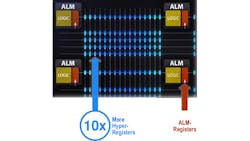

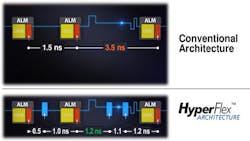

Altera’s new HyperFlex technology (Fig. 2) highlights another change in design to support high throughput. The change is critical because chips are larger and a signal can rarely get from one side of the chip to another as speeds increase. It is just a physical limitation. HyperFlex adds a host of Hyper-registers to facilitate pipelining of data through the FPGA connection fabric. Stratix 10 has 10 times the number of Hyper-Registers in the interconnect fabric than the previous FPGA designs.

Hyper-Registers are simply buffers that can be placed along a signal path to save data as it flows from a source to a sink (Fig. 3). Additional buffers increase the number of steps, but allow the overall clock rate to increase, thereby increasing overall system throughput.

Software optimizations using this technique include Hyper-Retiming, Hyper-Pipelining, and Hyper-Optimization, which are part of the new SpectraQ engine in Altera’s Quartus II FPGA design tool (see “FPGA Design Tool Takes Hierarchical Approach”). The addition of more Hyper-Registers increases system complexity, but the tools make their use transparent to designers so design time is actually reduced.

The approach can also help reduce power requirements. Some applications see as much as a 70% power reduction due to this and other enhancements in the Stratix 10 family. For example, sometimes the bus width can be cut in half while doubling the clock frequency, resulting in a 50% space reduction.

The Secure Device Manager (SDM) is part of Altera’s security support. This includes sector-based authentication and encryption allowing sections of the FPGA to be programmed using different security methods and keys. SDM supports multi-factor authentication and incorporates Physically Unclonable Function (PUF) technology. ARM Trust Zone technology is included with hard-core processor support.

Stratix 10 targets high-performance applications so the 1.5 GHz, quad-core Cortex-A53 is a good match for programmatic application aspects. The 64-bit cores include NEON SIMD and floating point support. Four cores share a 1 Mbyte L2 cache with ECC support.

The FPGAs are also designed to work with Altera’s Enpirion power solutions. The EM1130 PowerSoC supports the Stratix 10 SmartVoltage ID power management.