Intel's AVX Scales To 1024 bit Vector Math

The XMM register set gets expanded to 256 bits

Intel's SSEx (Streaming SIMD Extensions) started in 1999 with the Pentium III and have since grown to the latest incarnation dubbed AVX for Advanced Vector Extensions. AVX is expected in Intel's upcoming Sandy Bridge processor family. AVX is only one of a number of improvements for the upcoming 32nm chips but it addresses a number of significant issues including AES encryption.

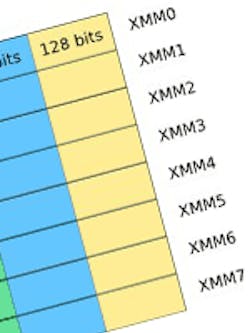

The width of the XMM (eXtended MultiMedia) register set has also increased from 128- to 256-bits. AVX is designed to handle 512-bit and 1024-bit registers. The number of registers remains fixed at 8. This allows backwards compatibility and limits the impact on applications, compilers and operating systems.

The vector instruction set architecture (ISA) is relatively indepedent of the CPU's normal ISA. SSE2 includng many new instructions including a set of cache control instructions designed to minimize cache pollution. SSE3 added DSP and 3D operations. It also implemented floating point to integer conversion without the need to change the global rounding mode. SSE4 incorported a number of packing and packed arithmetic instructions for advanced text processing as well as a CRC32 instruction. And now there is AVX.

The AVX enhancements include a number of instructions that do not target multimedia applications directly. For example, the AES support is for encryption and authentication that will make a significant impact in communication applications. Likewise, the PCMULQDQ instruction performs a carry-less multiplication. It is designed for advanced block cipher encryption. Other new instructions include broadcast permute, and a fused-multiply-add. AVX now includes hundreds of instructions with mnemonics only a compiler writer can love.

The register size increase provides support for 256-bit floating point numbers. This provides better performance as well as better overall power efficiency. It also support 3 and 4 operands. Often the XMM0 register is used implicitly. Different versions of AVX will be designated by the register width. The new incarnations are referred to as AVX-128 and AVX-256. Existing assembler instruction mnemonics that utilized the extended registers will be prefixed with VEX. As with SSE, they are upward compatible.

Intel's AVX-256 ups the ante for vector processing in general, multimedia processing specifically and now encryption. It will have a major impact on high performance compute applications as well as improving performance on the desktop and servers in general. Intel compilers will have support for AVX and most third party compilers will follow suite as they have in the past. Most will have updated versions prior to general availability of new hardware that is expected later this year.

About the Author

William G. Wong

Senior Content Director - Electronic Design and Microwaves & RF

I am Editor of Electronic Design focusing on embedded, software, and systems. As Senior Content Director, I also manage Microwaves & RF and I work with a great team of editors to provide engineers, programmers, developers and technical managers with interesting and useful articles and videos on a regular basis. Check out our free newsletters to see the latest content.

You can send press releases for new products for possible coverage on the website. I am also interested in receiving contributed articles for publishing on our website. Use our template and send to me along with a signed release form.

Check out my blog, AltEmbedded on Electronic Design, as well as his latest articles on this site that are listed below.

You can visit my social media via these links:

- AltEmbedded on Electronic Design

- Bill Wong on Facebook

- @AltEmbedded on Twitter

- Bill Wong on LinkedIn

I earned a Bachelor of Electrical Engineering at the Georgia Institute of Technology and a Masters in Computer Science from Rutgers University. I still do a bit of programming using everything from C and C++ to Rust and Ada/SPARK. I do a bit of PHP programming for Drupal websites. I have posted a few Drupal modules.

I still get a hand on software and electronic hardware. Some of this can be found on our Kit Close-Up video series. You can also see me on many of our TechXchange Talk videos. I am interested in a range of projects from robotics to artificial intelligence.

Voice Your Opinion!

To join the conversation, and become an exclusive member of Electronic Design, create an account today!

Leaders relevant to this article: