Many devices in the Internet of Things (IoT) are battery-operated or they may even use power-scavenging systems. The bottom line is that the process tends to be the part of the system using the most power, so optimizing how it uses power is critical.

The typical way to minimize power requirements is to run at full speed for as little time as possible and power down at other times. These days, most micros have a range of power-down modes with different power-utilization features that developers can take advantage of depending on the application. Some may only need to run the real-time clock (RTC), while others may have to maintain some or all of the RAM contents.

These methods usually help with almost any microcontroller, but what other options do developers have when choosing a low power platform?

Chip Design

Microcontroller chip designers generally choose technologies that will minimize power requirements while providing performance. Each iteration tends to improve power utilization, but some techniques offer significant advantages over the conventional method.

Eta Compute takes an asynchronous approach versus the conventional clocked design. The challenge with a clocked design is that it’s always cycling, and thus consumes power while in this mode. Eta’s design, with its Cortex-M3 and spiking neural-network support, takes advantage of this approach. The machine-learning (ML) ASIC consumes less power than most Cortex-M3 platforms.

Another approach is applied by Ambiq Micro for its Apollo 2. Its Subthreshold Power Optimized Technology (SPOT) platform uses transistors biased in the subthreshold region of operation. This allows the Cortex-M4F to consume less power than most Cortex-M3 implementations. Floating-point support is included. A Bluetooth version of the chip is available, too.

The challenge with both approaches is that the design process is more difficult than the conventional chip design. New design libraries help, but at this point, the technologies have been applied to a limited number of chips. Nonetheless, both hit the sweet spot for IoT devices.

Memory Design

Texas Instruments’ (TI) 16-bit MSP430 family has been known for its low-power operation. The family includes a wide variety of chips that target specific sensor and control applications.

One feature found in in the TI MSP430 FRAM (ferroelectric RAM) group of chips is FRAM memory. This non-volatile memory technology doesn’t have the speed and lifetime limitations that bog down flash memory. It was originally used for data storage, but now TI has chips with a unified memory for code and data, which creates significant flexibility in memory allocation.

Non-volatile data storage has other advantages for IoT environments where the processor runs only part of the time because data needn’t be stored in flash memory, or RAM doesn’t require battery backup. This allows the MSP430 to use very low power modes because the FRAM doesn’t need power to maintain its contents. Not having to move data to and from flash storage means startup and shutdown is faster, which also reduces power requirements.

FRAM is exclusive to TI’s MSP430, but a competitor looms on the horizon. Magnetoresistive RAM (MRAM) shares FRAM’s features compared to flash memory. Standard MRAM microcontrollers aren’t available yet, but the foundries used by fabless micro vendors are now including MRAM as part of their standard fare.

Processor Offload

Smart peripherals are another way to limit power consumption by allowing data acquisition and transfer while the processor is in sleep mode. A smart I2C slave device may have built-in address recognition, allowing it to wake up the processor when the device is selected.

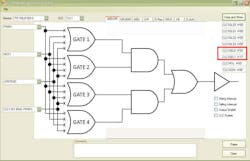

The other way to build smart peripherals is to link multiple peripherals together. For example, Microchip’s Configurable Logic Cell (CLC) can tie the outputs from peripherals to the input of another peripheral or interrupt. With the CLC configuration tool (see figure), designers can generate designs quickly and easily.

Most microcontroller vendors have a variation of CLC for their chips. STMicroelectronics calls its implementation “autonomous peripherals.” NXP’s term for intelligent peripheral management is FlexIO. And Silicon Labs has its Peripheral Reflex System (PRS). NXP has its own set of configurable peripherals.

Cirrus Logic’s PSoC takes configuration to the extreme with near FPGA flexibility. Not only can designers configure the linkage between peripherals, but also the peripherals themselves. PSoC chips come with a set of digital and analog blocks that can be configured into a range of standard and custom peripherals.

Power efficiency is affected by numerous aspects of a design, including the processor and its memory, peripherals, and their configuration. Developers will need to consider all of these aspects when selecting a device to meet the cost and lifetime requirements of a system.