New PSoC 6 Sports Dual, Asymmetric 32-bit Cores with Enhanced Security

Cypress Semiconductor’s PSoC was revolutionary when it first came out. It used a proprietary 8-bit core that was surrounded by configurable digital and analog blocks. This allowed a single stock keeping unit (SKU) to deliver an amazing combination of peripherals based upon the application and how the developer decided to configure the system. One design might use a digital block for a timer while another might use it as a custom serial interface. The PSoC family has grown using different cores and now employ ARM Cortex-M cores.

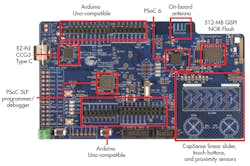

The PSoC 6 is Cypress’ latest offering, revealed at Embedded World 2017, and it’s almost as revolutionary as the original PSoC. It is available in a dual-core configuration with a Cortex-M0+ and a Cortex-M4 (Fig. 1). A single Cortex-M4 core version will also be available. The dual-core system allows one core to operate as a security processor with full control over the other core and peripheral access.

The PSoC 6 story is more about the dual-core solution. It still has the configurable digital and analog blocks, and there are improvements, but the dual-core approach has major implications for security and low-power operation. The 150-MHz Cortex-M4 has single precision floating point support and it is managed by the 100 MHz Cortex-M0+, which is designed to run in secure mode.

There is independent power management and interprocessor communication (IPC) hardware, plus shared SRAM support. The Cortex-M0+ can block the Cortex-M4’s access to blocks of memory and peripheral interfaces. The system can use as little as 200-µA. MCU active power is 22 μA/MHz. Deep sleep mode cuts power consumption down to 4.5 μA.

The Cortex-M0+ manages the Trusted Execution Environments (TEE). These are multiple hardware-based, secure enclaves. The hardware security support also includes secure boot, secure key storage, and a real hardware random number generator that uses the CapSense interface for randomization. Each chip has a unique ID, as well.

The system will support HyperBus and SD card support in future versions, but it already uses QSPI for eXecute-in-place (XIP) support using encrypted or unencrypted, off-chip storage. On-chip flash up to 1 Mbyte will be available. RAM tops out at 288 Kbytes. Each core has an 8 Kbyte cache.

Analog support is significant, with an on-chip buck converter to a 12-bit ADC and DAC. The initial chips will have a pair of op amps and two comparators. The PSoC 6 will have a range of wireless options, starting with Bluetooth Low Energy 5.0 (BLE) and moving into other technologies like Wi-Fi.

The initial PSoC 6 develop kit (Fig. 2) is impressive as well. Of course, it has a PSoC 6 and a PSoC 5 to handle programming. It has a USB Type-C interface that provides a high-speed interface and it also supports a power usage model where external power can be routed through Type-C connector. The Type-C support is actually independent of PSoC 6 and provided by Cypress EZ-PD chips. One advantage the board has over previous platforms is that it can measure the power utilization of just the PSoC 6

The board is compatible with Arduino Uno modules. It has a 512 Mbit QSPI NOR flash chip and an on-board antenna for the Bluetooth support. The Capsense touch support includes a section that can be used for a range of buttons and sliders.

The PSoC 6 supported by a range of software including PSoC Creator. There is also a common peripheral library that allows most of the PSoC features to be utilized without dealing with most customized chip design tools.

About the Author

William G. Wong

Senior Content Director - Electronic Design and Microwaves & RF

I am Editor of Electronic Design focusing on embedded, software, and systems. As Senior Content Director, I also manage Microwaves & RF and I work with a great team of editors to provide engineers, programmers, developers and technical managers with interesting and useful articles and videos on a regular basis. Check out our free newsletters to see the latest content.

You can send press releases for new products for possible coverage on the website. I am also interested in receiving contributed articles for publishing on our website. Use our template and send to me along with a signed release form.

Check out my blog, AltEmbedded on Electronic Design, as well as his latest articles on this site that are listed below.

You can visit my social media via these links:

- AltEmbedded on Electronic Design

- Bill Wong on Facebook

- @AltEmbedded on Twitter

- Bill Wong on LinkedIn

I earned a Bachelor of Electrical Engineering at the Georgia Institute of Technology and a Masters in Computer Science from Rutgers University. I still do a bit of programming using everything from C and C++ to Rust and Ada/SPARK. I do a bit of PHP programming for Drupal websites. I have posted a few Drupal modules.

I still get a hand on software and electronic hardware. Some of this can be found on our Kit Close-Up video series. You can also see me on many of our TechXchange Talk videos. I am interested in a range of projects from robotics to artificial intelligence.

Voice Your Opinion!

To join the conversation, and become an exclusive member of Electronic Design, create an account today!

Leaders relevant to this article: