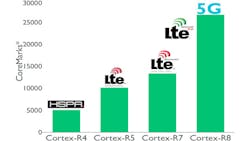

5G is still on the horizon, but ARM’s new Cortex-R8 has arrived to handle this more demanding application (Fig. 1). It follows from the Cortex-R4, -R5, and -R7 that have addressed the needs of automotive, LTE, and LTE Advanced applications. The Cortex-R8 provides a significant performance boost needed to handle 5G.

The Cortex-R8 uses an 11-stage pipeline with a super scalar, out-of-order (OoO) architecture based on the ARMv7-R standard. It supports up to four cores and each core can have up to 2 Mbytes of tightly coupled memory (TCM). Memory and buses are protected by ECC and parity.

The TCM can be used for cache and local memory so deterministic interrupt routines can be contained in it. The Cortex-R architecture supports a low-latency interrupt mode (LLIM). The memory protection unit handles up to 16 regions.

The hardware supports SIMD instructions for very high-performance DSP and media functions. The architecture supports IEEE754 double-precision and single-precision floating point.

The Cortex-R family supports lock-step mode (see “Multicore Processor Tackles SMP, AMP and Lock Step Mode” on electronicdesign.com). This links a pair of cores. It is useful in safety-critical and fault-tolerant applications and it can be applied on a per-core basis. Systems can be configured in asymmetric multi-processing (AMP) mode or symmetric multi-processing (SMP) mode.

About the Author

William G. Wong

Senior Content Director - Electronic Design and Microwaves & RF

I am Editor of Electronic Design focusing on embedded, software, and systems. As Senior Content Director, I also manage Microwaves & RF and I work with a great team of editors to provide engineers, programmers, developers and technical managers with interesting and useful articles and videos on a regular basis. Check out our free newsletters to see the latest content.

You can send press releases for new products for possible coverage on the website. I am also interested in receiving contributed articles for publishing on our website. Use our template and send to me along with a signed release form.

Check out my blog, AltEmbedded on Electronic Design, as well as his latest articles on this site that are listed below.

You can visit my social media via these links:

- AltEmbedded on Electronic Design

- Bill Wong on Facebook

- @AltEmbedded on Twitter

- Bill Wong on LinkedIn

I earned a Bachelor of Electrical Engineering at the Georgia Institute of Technology and a Masters in Computer Science from Rutgers University. I still do a bit of programming using everything from C and C++ to Rust and Ada/SPARK. I do a bit of PHP programming for Drupal websites. I have posted a few Drupal modules.

I still get a hand on software and electronic hardware. Some of this can be found on our Kit Close-Up video series. You can also see me on many of our TechXchange Talk videos. I am interested in a range of projects from robotics to artificial intelligence.

Voice Your Opinion!

To join the conversation, and become an exclusive member of Electronic Design, create an account today!

Leaders relevant to this article: