Micro Targets Telematics With 3D And HyperBus Support

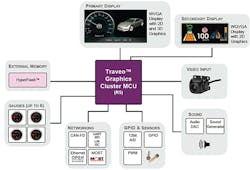

Spansion’s Traveo (Fig. 1) mixes 400 DMIPS ARM Cortex-R5 core with 3D graphics and Spansion’s HyperBus (see “How HyperBus Delivers 330 Mbyte/s Using A Dozen Signals”) to target automotive telematics applications. The single chip solution addresses the range of telematics chores including support for a rear-view camera, multiple displays and networking.

The Traveo family can handle CAN-FD, MOST and Ethernet AVB (audio video bridging). It can handle display interfaces like LVDS and RSDS. The system also provides high-end audio support. A 12-bit ADC and GPIO provide additional peripheral functionality.

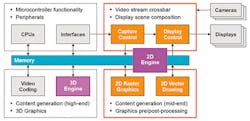

The graphics engine (Fig. 2) handles 2D and 3D chores including camera input. The hardware surface image generation allows 3D presentation without the need for a costly frame buffer. The system also has Bezier curve and fill functions in hardware to support smother text display. The HyperBus interface provides access to off-chip flash and RAM providing access to more graphic content.

The HyperBus matches the low cost target for the Traveo. HyperBus utilizes fewer interface pins allowing the use of lower cost flash and RAM storage. HyperBus can deliver 330 Mbytes/s compared to under 100 Mbytes/s for QSPI, the other low pin-count memory option.

Traveo also incorporates Spansion’s Secure Hardware Extensions (SHE). This includes secure boot, AES support, message authentication code (MAC) support and a random number generator (RNG).