Multicore Separation Architecture Reduces Safety Software Complexity

ARM’s Cortex-R series takes on a range of applications from safety critical systems like automotive driver assistance systems (ADAS) to 5G wireless. The Cortex-R provides a deterministic platform like the Cortex-M that does not include features like virtual memory and virtual machine (VM) support found in the Cortex-A series. The Cortex-R platform adds additional safety and reliability features like the ability to link two cores in a lockstep mode.

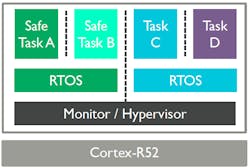

ARM’s latest Cortex-R52 architecture extends the Cortex-R series to include partitioned systems (Fig. 1) that can help reduce software complexity by allowing developers to isolation operating systems applications. This approach is common on the Cortex-A series with its VM hypervisor support, but that is impractical in an environment where determinism is a primary requirement. Even virtual memory support cannot be used in this environment, because a cache miss results in a non-determinant delay to retrieve information.

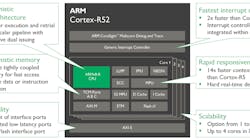

The Cortex-R52 is a 32-bit platform with up to four cores (Fig. 2). Multiple cores can be linked in lock-step mode or used independently. The system uses a shared address space and a new mode is added to manage the partition system that is logically like the VM support on the Cortex-A. The main difference is the use of a memory management unit (MMU) with single memory space for deterministic access. A partition has system limited memory access and an ID that can be utilized by peripheral IP in a chip.

The Cortex-R52 improves on the interrupt and context switching of the Cortex-R5. The Cortex-R52 is twice as fast on interrupt response and 14 times faster for context switching.

The Cortex-R family is designed for functional safety oriented applications like automotive, industrial, and healthcare. The Cortex-R52 addresses standards like IEC 61508, ISO 26262, IEC 60601, EN 50129, and DO-254. It has ECC on internal memory and buses. The system comes with software BIST (built-in self-test) libraries.

The Cortex-R52 represents a major step forward in safety and high-reliability embedded computing. It will allow multiple applications and real time operating systems to be run simultaneously in isolated environments. As well, it will allow consolidation of hardware for critical applications like ADAS.