100 ARM Cortex-A53 Cores on One Chip

EZchip’s TILE-Gx packs up to 72 64-bit VLIW RISC cores along with eight 10 Gbit Ethernet ports, making an excellent platform for Software Defined Networking (SDN) and Network Function Virtualization (NFV) using its mPIPE (multicore Programmable Intelligent Packet Engine) packet processing front end (see “Single Chip Packs in 100 VLIW Cores”). The family supports Zero-Overhead Linux (ZOL), a tickless kernel feature for real-time operation.

The TILE-Gx has found a home in platforms like VadaTech’s AMC740 (Fig. 1). Advanced Mezzanine Cards (AMCs) are often used in MicroTCA systems for communication applications. The AMC740 front panel exposes four 10-Gbit Ethernet LC ports. The board has four banks of DDR3 64-bit memory with ECC and a bank of flash memory. The PCI Express x8 ports are available on the backplane connector.

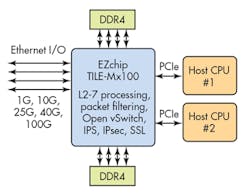

One the drawing board is EZchip’s TILE-Mx that swaps out the custom VLIW RISC core for a 64-bit ARM Cortex-A53. EZchip also ups the ante with 100 cores and support for 100 G Ethernet in the TILE-Mx100 (Fig. 2). The chip also supports various combinations of 1 G, 10 G, 25 G, 40 G, and 50 G Ethernet. EZchip’s original claim to fame was network processing units (NPUs), so it has extensive networking expertise that it added to Tilera’s already impressive network accelerators. The TILE-Mx100 delivers 200 Gbits/s of throughput.

Internally the TILE-Mx has a 3-level, coherent, 40 Mbyte of cache courtesy of the SkyMesh architecture and access to 1 Tbyte of DDR4 memory. There is a 5-level hierarchical Traffic Manager with 256,000 queues that feeds the MiCA engine for over 100 Gbit/s of crypto acceleration. There is even precision packet time stamping with IEEE1588v2 support.

This file type includes high resolution graphics and schematics when applicable.

Packing lots of 64-bit ARM cores on a chip is not unique. Cavium’s ThunderX scales up to 48 2.5 GHz, 64-bit ARMv8 cores (see “64-Bit Cortex Platform to Take on x86 Servers in the Cloud”). Cavium builds its multicore fabric around the Cavium Coherent Processor Interconnect (CCPI) and surrounds it with network accelerators.

Of course, Broadcom has been delivering massive, multicore chips as well that can be combined into larger fabrics. The XLP900 series had 80 MIPS64 cores. The external interconnect allowed a system with up to 640 cores to be constructed. This was in 2013. The Broadcom XLP II family utilizes 3 GHz ARMv8-a cores. Notice a trend here?

Unfortunately, getting your hands on a TILE-Mx100 will take a little time since samples will not be ready until next year. In the meantime, the AMC740 is available now as is the ThunderX and Broadcom’s offerings. Many ARMs help finish jobs quickly.